# ABT Advanced BiCMOS Technology A High-Performance Line of 5-V and 3.3-V Products

# Data Book

DOCUMENT COMING UERASS

| L | General Information                              | 1  |

|---|--------------------------------------------------|----|

|   |                                                  |    |

|   | ABT Octals                                       | 2  |

|   |                                                  |    |

|   | ABT Widebus™                                     | 3  |

|   | ABT Widebus+™                                    | 4  |

|   | ABT Memory Drivers                               | 5  |

|   | <del></del>                                      |    |

|   | ABT 25- $\Omega$ Incident-Wave Switching Drivers | 6  |

|   | Futurebus+/BTL Transcelvers                      | 7  |

|   | JTAG SCOPE™ Testability Devices                  | 8  |

|   | LVT Octals                                       | 9  |

|   | LVT Widebus™                                     | 10 |

|   |                                                  |    |

|   | Application Notes and Articles                   | 11 |

|   | ABT Characterization Information                 | 12 |

|   | Mechanical Data                                  | 13 |

.

# ABT Advanced BiCMOS Technology Data Book

1992

A High-Performance Line of 5-V and 3.3-V Products

### IMPORTANT NOTICE

Texas Instruments Incorporated (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Please be aware that TI products are not intended for use in life-support appliances, devices, or systems. Use of TI product in such applications requires the written approval of the appropriate TI officer. Certain applications using semiconductor devices may involve potential risks of personal injury, property damage, or loss of life. In order to minimize these risks, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. Inclusion of TI products in such applications is understood to be fully at the risk of the customer using TI devices or systems.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1992, Texas Instruments Incorporated

Printed in the U.S.A.

EPIC, EPIC-IIB, SCOPE, UBE, UBT, Widebus, Shrink Widebus, and Widebus+ are trademarks of Texas Instruments Incorporated.

### INTRODUCTION

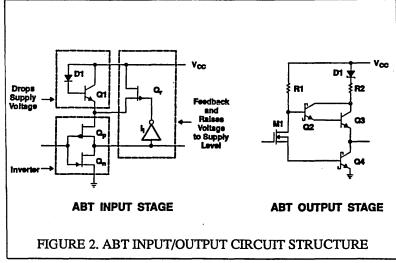

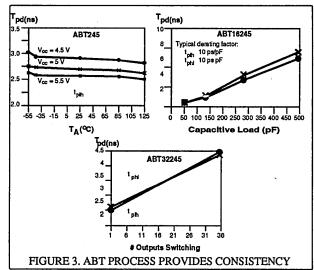

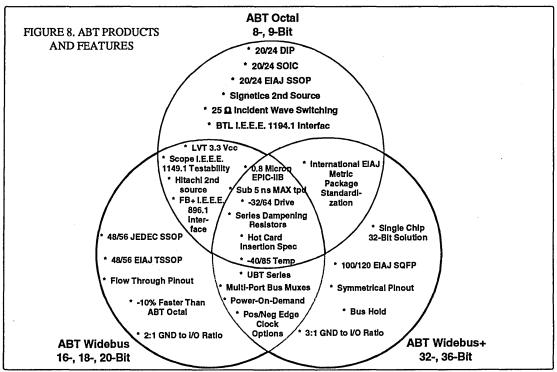

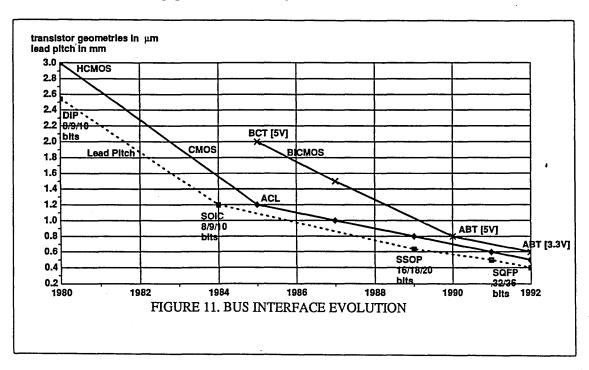

As the operating frequencies of microprocessors increase, the period of time allotted for memory access, arithmetic computation, or similar operations decreases. With this in mind, a new series of advanced bus interface products, developed with Texas Instruments' submicron Advanced BiCMOS (ABT) process technology, assumes a prominent role as the key high-performance logic needed in today's workstation, personal and portable computer, and telecom systems. The goal of this family of products is to provide to system designers a bus interface solution combining high drive capability, lower power consumption, signal integrity, and propagation delays fast enough to appear transparent with respect to overall system performance. Fine-pitch package options simplify layout, reduce required board space, and decrease overall system costs. Novel circuit design techniques add value over competitive solutions.

Welcome to the new Texas Instruments ABT Advanced Bus Interface Data Book. Included herein is the broadest line of advanced bus products in the industry. Some of the products can be considered general purpose, while others are designed to offer specific compatibility to IEEE standard specifications. For the first time, 3.3-V products have been included along with traditional 5-V offerings. However, the one feature common to all the products is performance in the form of the EPICIIB™ submicron ABT process. It is part CMOS and part bipolar, but it is all performance.

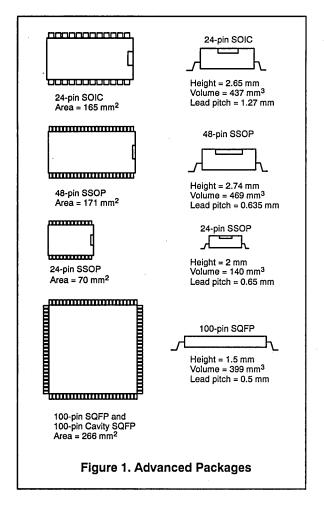

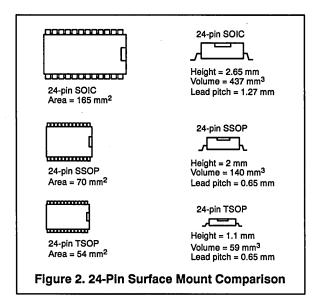

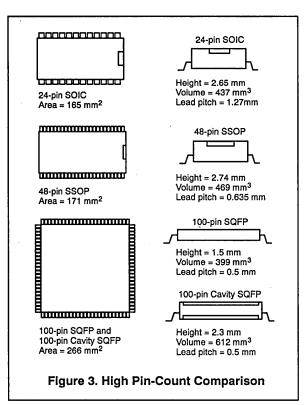

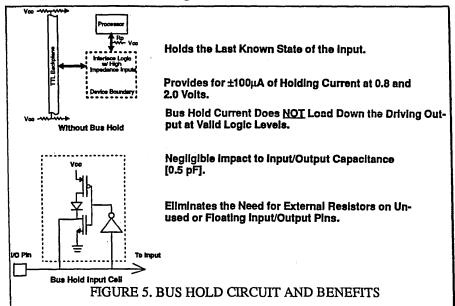

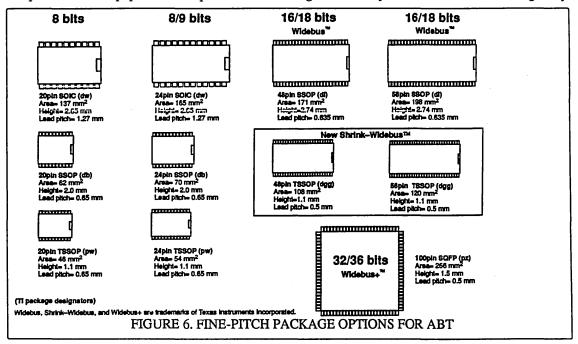

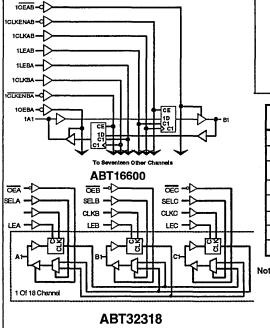

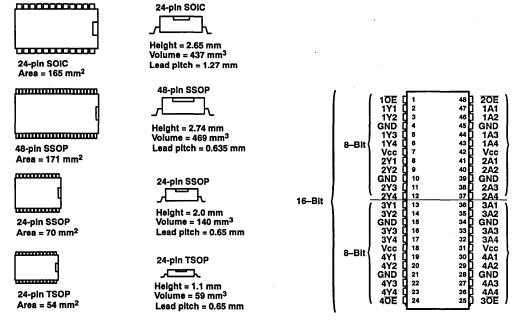

The products described in this data book have been designed specifically to help system engineers meet the varied and stringent requirements of their end equipments. Products range from the extremely simple and popular octal buffer/transceiver to the extremely complex 36-bit universal bus transceiver (UBT™). For midscale integration, a whole series of 16-bit Widebus™ products exist. Because board costs also affect system costs, it is desirable for chips to be housed in a variety of packaging options to save space. Each of the products in the data book are offered in a number of different surface-mount and fine-pitch package options such as the shrink small-outline package (SSOP) and the thin shrink small-outline package (TSSOP). Finally, circuit design techniques built into the silicon such as mixed mode, power on demand, and bus hold offer enhanced parametrics and save having to discretely implement these enhancements.

Most of the products in the data book are available in production quantities. Please contact your local authorized distributor or Texas Instruments representative for details on any of these devices. Some of the devices in this data book are not yet available in production quantities; information on these devices is included in Product Previews. Texas Instruments is also evaluating many other devices for market introduction. Some of these are listed along with a description of their function in tables at the front of each section. Please contact our hotline at 214-997-5202 if you are interested in learning more about our plans for these devices.

Finally, in addition to specific information on the products, the data book contains other useful sections including mechanical data, application notes, and characterization information.

We hope you agree that Texas Instruments has the most complete line of high-performance bus-interface logic in the industry. We hope that these products will meet your system and design needs.

EPIC-IIB, UBT, and Widebus are trademarks of Texas Instruments Incorporated.

### PRODUCT STAGE STATEMENTS

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

The next statements must be used in combination:

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

If any of the pages contain PRODUCT PREVIEW information, this statement must appear at the lower left on those pages:

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

If any of the pages contain ADVANCE INFORMATION, this statement must appear at the lower left on those pages:

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

# **Contents**

|                                                                                                                                          | Page                       |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Section 1 – General Information                                                                                                          | 1-1                        |

| Alphanumeric Index Glossary Explanation of Function Tables D Flip-Flop and Latch Signal Conventions Thermal Information Functional Index | 1–5<br>1–8<br>1–10<br>1–11 |

| 5-V ADVANCED BUS-INTERFACE AND MANAGEMENT LOGIC                                                                                          |                            |

| Section 2 – ABT Octals                                                                                                                   | 2-1                        |

| 8-, 9-, and 10-Bit Product                                                                                                               | 2–2                        |

| Section 3 – ABT Widebus™                                                                                                                 | 3–1                        |

| 16-, 18-, and 20-Bit Product                                                                                                             | 3–2                        |

| Section 4 – ABT Widebus+™                                                                                                                | 4–1                        |

| 32- and 36-Bit Product                                                                                                                   | 4-2                        |

| Section 5 – ABT Memory Drivers                                                                                                           | 5–1                        |

| 8-, 9-, 10-, 11-, 12-, 16-, 18-, and 20-Bit Product                                                                                      | 5–2                        |

| Section 6 – ABT 25- $\Omega$ Incident-Wave Switching Drivers                                                                             | 6–1                        |

| 8-Bit Product                                                                                                                            | 6–2                        |

| Section 7 – Futurebus+/BTL Transceivers                                                                                                  | 7–1                        |

| 7-, 8-, 9-, and 18-Bit Product                                                                                                           | 7–2                        |

| Section 8 – JTAG SCOPE ™ Testability Devices                                                                                             | 8–1                        |

| 8-, 16-, 18-, and 20-Bit Product                                                                                                         | 8–2                        |

|                                                                                                                                          |                            |

| 3.3-V ADVANCED BUS-INTERFACE AND MANAGEMENT LOGIC                                                                                        |                            |

| Section 9 – LVT Octals                                                                                                                   | 9–1                        |

| 8-Bit Product                                                                                                                            | 9–2                        |

| Section 10 – LVT Widebus™                                                                                                                | 10-1                       |

| 16- and 18-Bit Product                                                                                                                   | 10–2                       |

# **Contents (continued)**

| •                                                                                         | Page  |

|-------------------------------------------------------------------------------------------|-------|

| Section 11 – Application Notes and Articles                                               | 11-1  |

| The Bypass Capacitor in High-Speed Environments                                           | 11–3  |

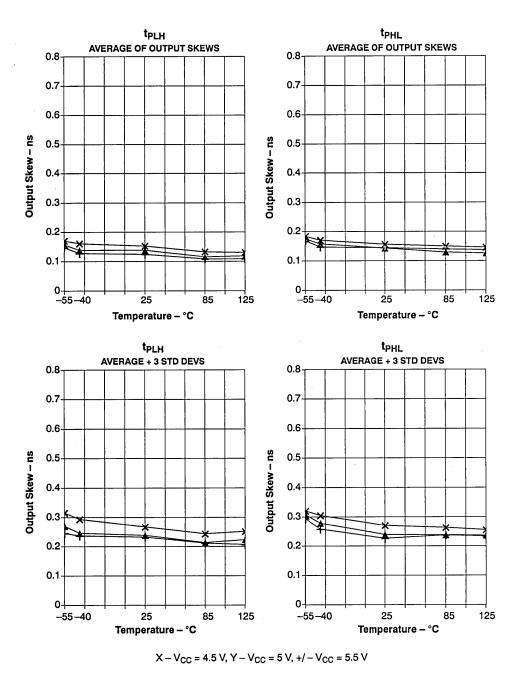

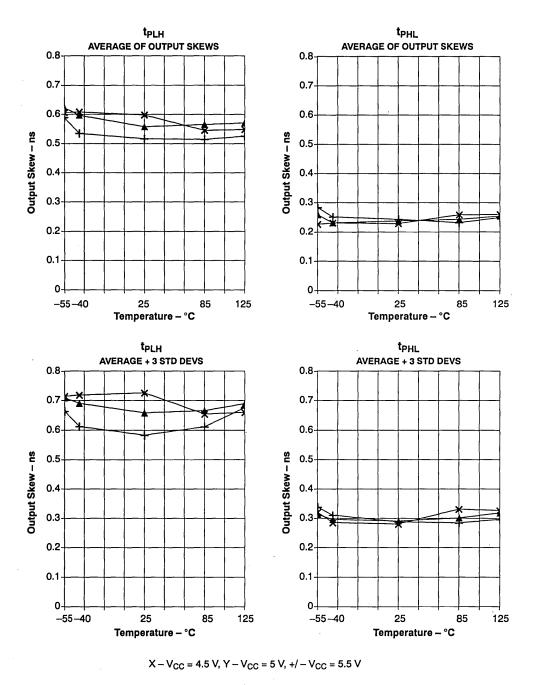

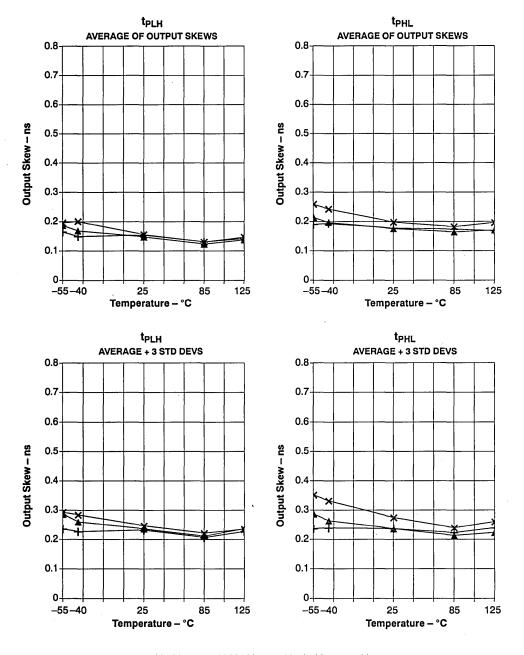

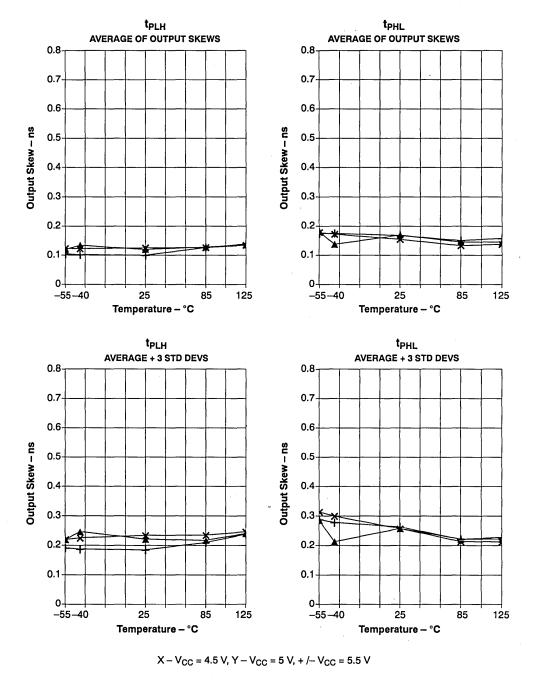

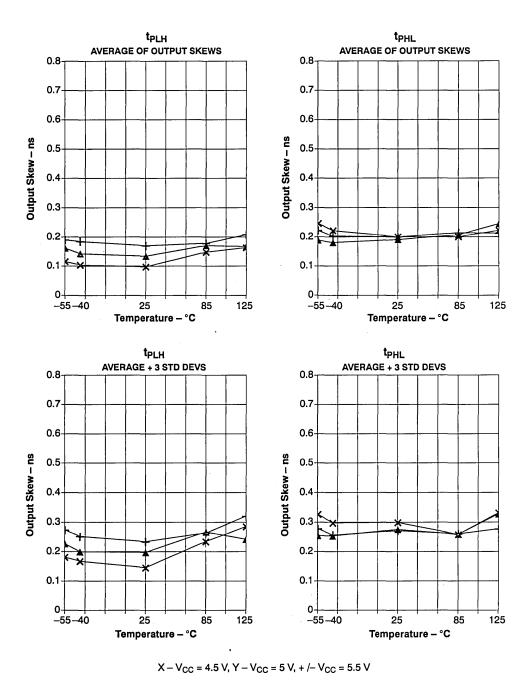

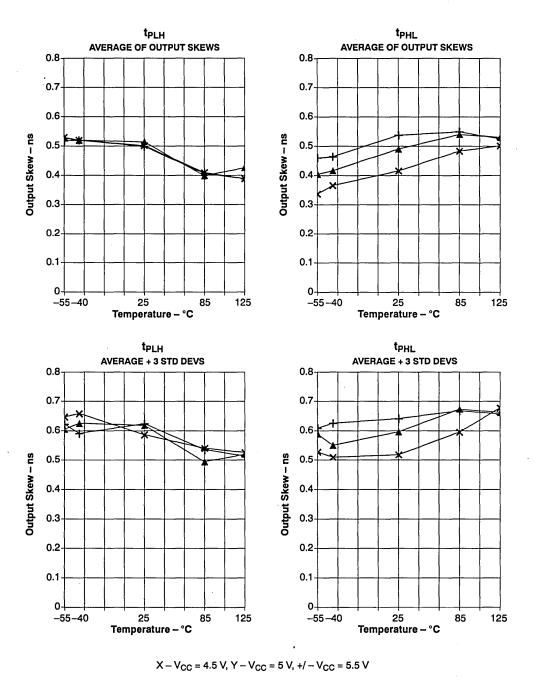

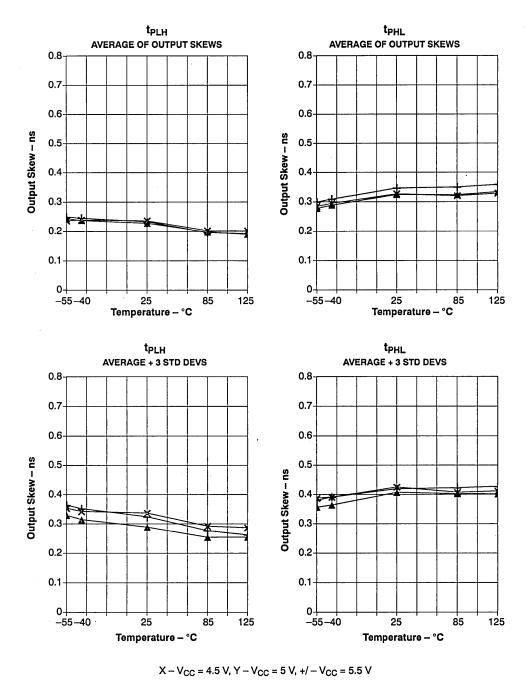

| Family of Curves Demonstrating Output Skews for Advanced CMOS Devices                     | 11-15 |

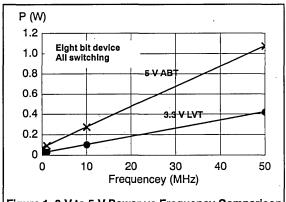

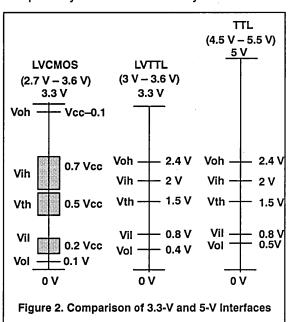

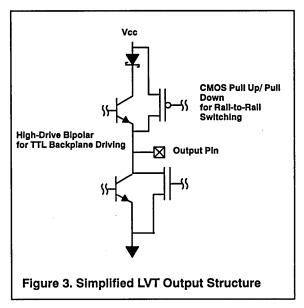

| Mixing It Up With 3.3 Volts                                                               | 11-29 |

| Package Thermal Considerations                                                            | 11–37 |

| Recent Advancements in Bus-Interface Packaging and Processing                             | 1147  |

| ABT Enables Optimal System Design                                                         | 11–55 |

| Section 12 – ABT Characterization Information                                             | 12–1  |

|                                                                                           |       |

| Section 13 – Mechanical Data                                                              | 13–1  |

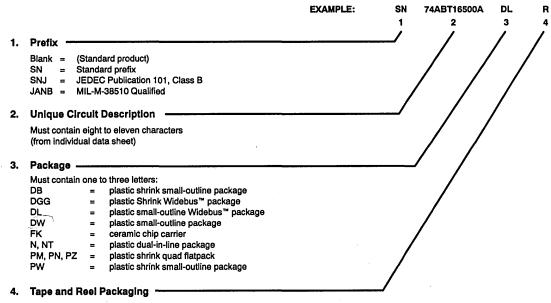

| Ordering Instructions                                                                     | 13–3  |

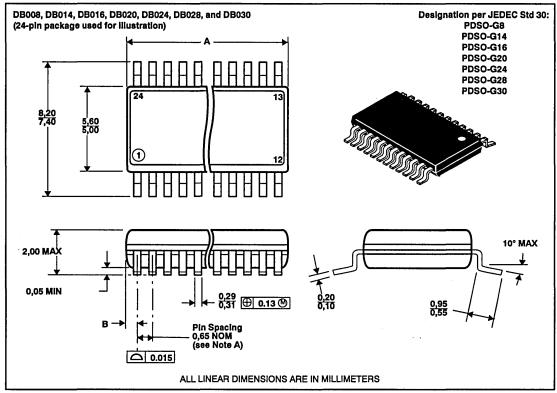

| DB008, DB014, DB016, DB020, DB024, DB028, and DB030 Plastic Shrink Small-Outline Packages | 13–4  |

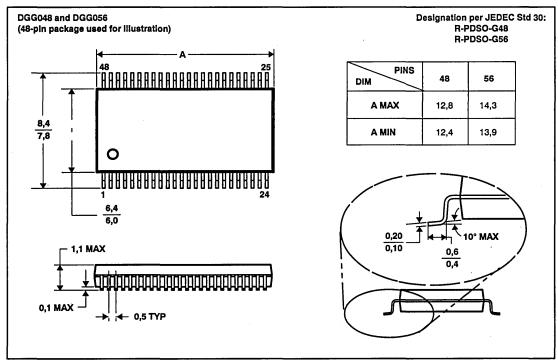

| DGG048 and DGG056                                                                         | 40.5  |

| Plastic Shrink Widebus™ Packages                                                          | 13–5  |

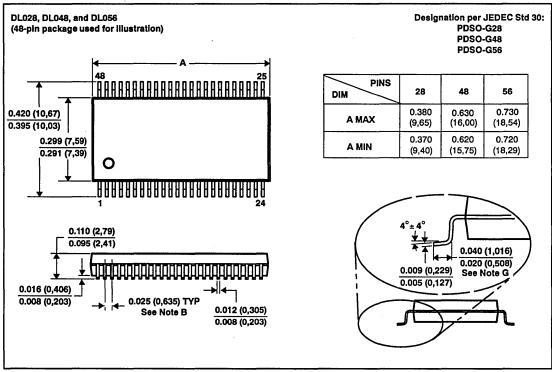

| DL028, DL048, and DL056 Plastic Small-Outline Widebus™ Packages                           | 13-6  |

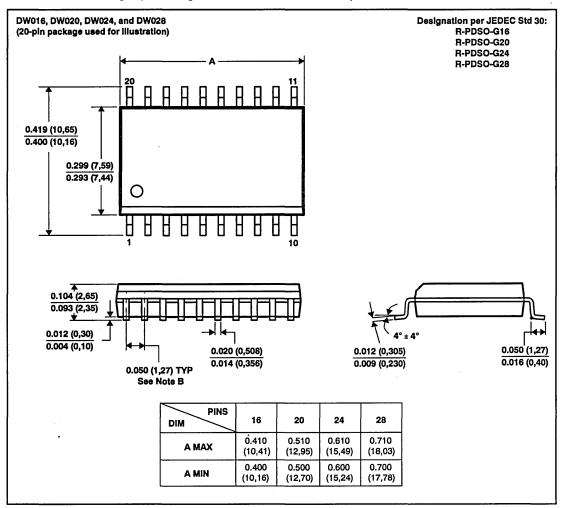

| DW016, DW020, DW024, and DW028                                                            | 40.7  |

| Plastic Small-Outline Packages                                                            | 13–7  |

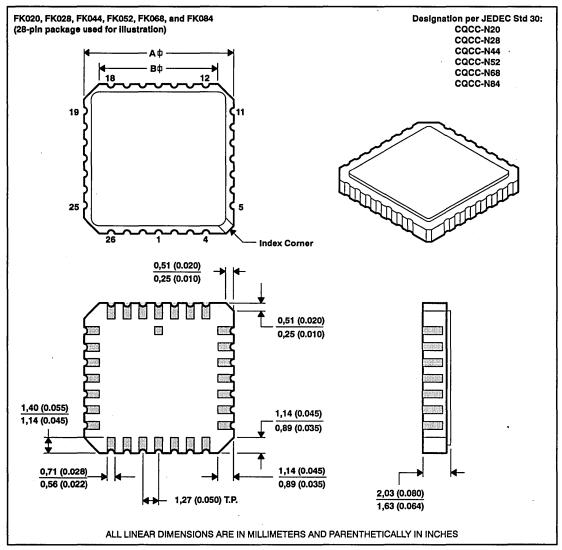

| FK020, FK028, FK044, FK052, FK068, and FK084  Ceramic Chip Carriers                       | 13–8  |

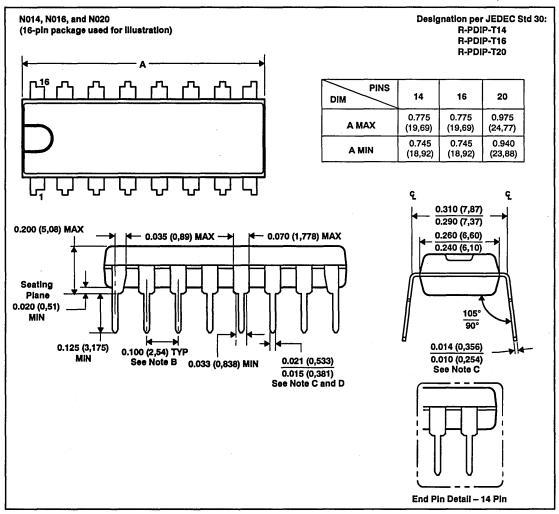

| N014, N016, and N020 300-mil Plastic Dual-in-Line Packages                                | 13–10 |

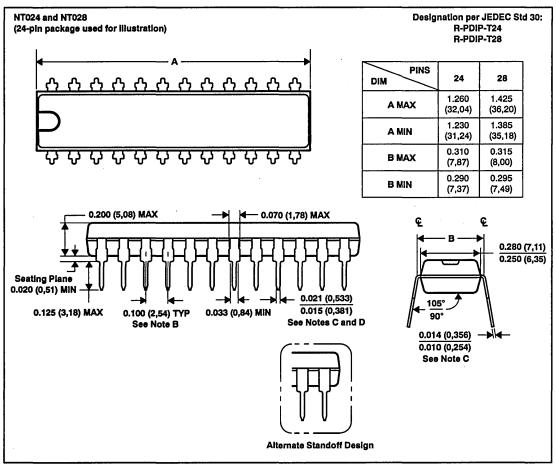

| NT024 and NT028 600-mil Plastic Dual-in-Line Packages                                     | 13–11 |

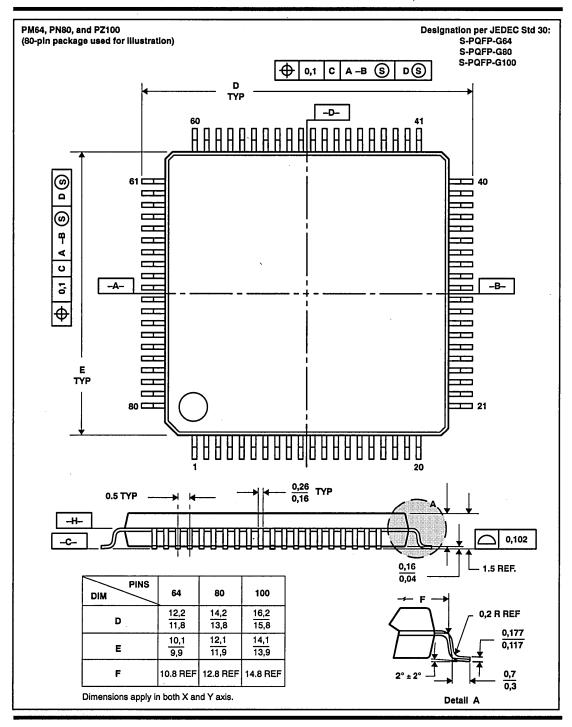

| PM64, PN80, and PZ100 JEDEC Metric Plastic Shrink Quad Flatpacks                          | 13–12 |

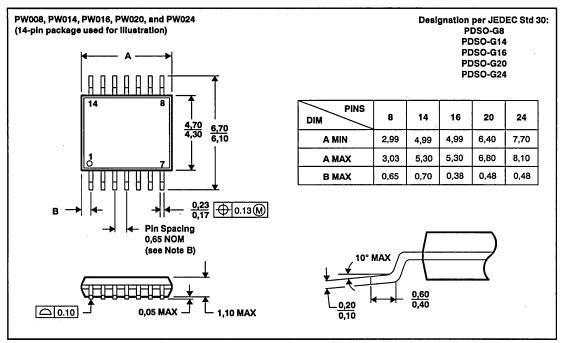

| PW008, PW014, PW016, PW020, and PW024 Plastic Shrink Small-Outline Packages               |       |

| General Information                        |

|--------------------------------------------|

| ABT Octals 2                               |

| ABT Widebus™ 3                             |

| ABT Widebus+™ 4                            |

| ABT Memory Drivers 5                       |

| ABT 25-Ω Incident-Wave Switching Drivers 6 |

| Futurebus+/BTL Transceivers 7              |

| JTAG SCOPE™ Testability Devices            |

| LVT Octals 9                               |

| LVT Widebus™ 10                            |

| Application Notes and Articles             |

| ABT Characterization Information 12        |

| Mechanical Data                            |

# **ALPHANUMERIC INDEX**

| DEVIC             | CE                         | PAGE | DEVIC         | E             | PAGE           |

|-------------------|----------------------------|------|---------------|---------------|----------------|

| Advanced BICMOS T | echnology (ABT)            |      | SN54ABT8952   | SN74ABT8952   | . 8–53         |

| SN54ABT125        | SN74ABT125                 | 2–3  | SN54ABT16240  | SN74ABT16240  |                |

| SN54ABT126        | SN74ABT126                 | 2-7  | SN54ABT16241  | SN74ABT16241  |                |

| SN54ABT240        | SN74ABT240                 | 2-11 | SN54ABT16244  | SN74ABT16244  | . 3–15         |

| SN54ABT241        | SN74ABT241                 | 215  | SN54ABT16245  | SN74ABT16245  | . 3–21         |

| SN54ABT244        | SN74ABT244                 | 2-21 | SN54ABT16260  | SN74ABT16260  | . 3–25         |

| SN54ABT245        | SN74ABT245                 | 2-25 | SN54ABT16373  | SN74ABT16373  | . 3–33         |

| SN54ABT273        | SN74ABT273                 | 2-29 | SN54ABT16374  | SN74ABT16374  | . 3–39         |

| SN54ABT373        | SN74ABT373                 | 2–35 | SN54ABT16377  | SN74ABT16377  | . 3–45         |

| SN54ABT374        | SN74ABT374                 | 2-41 | SN54ABT16460  | SN74ABT16460  | . 3–51         |

| SN54ABT377        | SN74ABT377                 | 2-47 | SN54ABT16470  | SN74ABT16470  | . <b>3–</b> 59 |

| SN54ABT533        | SN74ABT533                 | 2–53 | SN54ABT16500A | SN74ABT16500A | . 3–67         |

| SN54ABT534        | SN74ABT534                 | 2-59 | SN54ABT16501  | SN74ABT16501  | . 3–75         |

| SN54ABT540        | SN74ABT540                 | 2–65 | SN54ABT16540  | SN74ABT16540  | . 3–83         |

| SN54ABT541        | SN74ABT541                 |      | SN54ABT16541  | SN74ABT16541  |                |

| SN54ABT543        | SN74ABT543                 | 1    | SN54ABT16543  | SN74ABT16543  | . 3–91         |

| SN54ABT544        | SN74ABT544                 |      | SN54ABT16600  | SN74ABT16600  | . 3–99         |

| SN54ABT573        | SN74ABT573                 | ľ    | SN54ABT16601  | SN74ABT16601  | . 3–105        |

| SN54ABT574        | SN74ABT574                 |      | SN54ABT16623  | SN74ABT16623  | . 3–111        |

| SN54ABT620        | SN74ABT620                 |      | SN54ABT16640  | SN74ABT16640  | . 3–117        |

| SN54ABT623        | SN74ABT623                 |      | SN54ABT16646  | SN74ABT16646  | . 3–121        |

| SN54ABT640        | SN74ABT640                 |      | SN54ABT16648  | SN74ABT16648  | . 3–129        |

| SN54ABT646        | SN74ABT646                 |      | SN54ABT16651  | SN74ABT16651  | . 3–137        |

| SN54ABT646A       | SN74ABT646A                |      | SN54ABT16652  | SN74ABT16652  | . 3–145        |

| SN54ABT651        | SN74ABT651                 | 1    | SN54ABT16657  | SN74ABT16657  | . 3–153        |

| SN54ABT652        | SN74ABT652                 |      | SN54ABT16821  | SN74ABT16821  |                |

| SN54ABT652A       | SN74ABT652A                |      | SN54ABT16823  | SN74ABT16823  |                |

| SN54ABT657        | SN74ABT657                 |      | SN54ABT16825  | SN74ABT16825  |                |

| SN54ABT821        | SN74ABT821                 |      | SN54ABT16826  | SN74ABT16826  |                |

| SN54ABT823        | SN74ABT823                 |      | SN54ABT16827  | SN74ABT16827  |                |

| SN54ABT827        | SN74ABT827                 |      | SN54ABT16828  | SN74ABT16828  |                |

| SN54ABT828        | SN74ABT828                 | J    | SN54ABT16833  | SN74ABT16833  |                |

| SN54ABT833        | SN74ABT833                 |      | SN54ABT16841  | SN74ABT16841  |                |

| SN54ABT841        | SN74ABT841                 |      | SN54ABT16843  | SN74ABT16843  |                |

| SN54ABT843        | SN74ABT843                 |      | SN54ABT16853  | SN74ABT16853  |                |

| SN54ABT853        | SN74ABT853                 | - 1  | SN54ABT16862  | SN74ABT16862  |                |

| SN54ABT861        | SN74ABT861                 |      | SN54ABT16863  | SN74ABT16863  |                |

| SN54ABT862        | SN74ABT862                 | i    | SN54ABT16952  | SN74ABT16952  |                |

| SN54ABT863        | SN74ABT863                 |      | SN54ABT162240 | SN74ABT162240 |                |

| SN54ABT2240       | SN74ABT2240                | ſ    | SN54ABT162244 | SN74ABT162244 |                |

| SN54ABT2241       | SN74ABT2241                | 1    | SN54ABT162260 | SN74ABT162260 |                |

| SN54ABT2244       | SN74ABT2244                | . [  | SN54ABT162500 | SN74ABT162500 |                |

| SN54ABT2245       | SN74ABT2245                |      | SN54ABT162501 | SN74ABT162501 |                |

| SN54ABT2952       | SN74ABT2952                |      | SN54ABT162600 | SN74ABT162600 |                |

| SN54ABT2952A      | SN74ABT2952A               | l    | SN54ABT162601 | SN74ABT162601 |                |

| SN54ABT2953       | SN74ABT2953                | j.   | SN54ABT18245  | SN74ABT18245  |                |

| SN54ABT5400       | SN74ABT5400                | 1    | SN54ABT18502  | SN74ABT18502  |                |

| SN54ABT5401       | SN74ABT5401<br>SN74ABT5402 | l h  | SN54ABT18504  | SN74ABT18504  |                |

| SN54ABT5402       |                            | - '  | SN54ABT18646  | SN74ABT18646  |                |

| SN54ABT5403       | SN74ABT5403                | 1    | SN54ABT18652  | SN74ABT18652  |                |

| SN54ABT8245       | SN74ABT8245                |      | SN54ABT25241  | SN74ABT25241  |                |

| SN54ABT8543       | SN74ABT8543                | F    | SN54ABT25244  | SN74ABT25244  |                |

| SN54ABT8646       |                            |      | SN54ABT25245  | SN74ABT25245  |                |

| SN54ABT8652       | SN74ABT8652                | 0-43 | SN54ABT32245  | SN74ABT32245  | . 4–3          |

## **ALPHANUMERIC INDEX**

| DEVIC               | DE .                        | PAGE    |

|---------------------|-----------------------------|---------|

| Advanced BICMOS T   | echnology (ABT) (continued) |         |

| SN54ABT32316        | SN74ABT32316                | . 4–9   |

| SN54ABT32318        | SN74ABT32318                | . 4–17  |

| SN54ABT32373        | SN74ABT32373                | . 4–25  |

| SN54ABT32374        | SN74ABT32374                | . 4–31  |

| SN54ABT32500        | SN74ABT32500                | . 4–37  |

| SN54ABT32501        | SN74ABT32501                | . 4–43  |

| SN54ABT32543        | SN74ABT32543                | . 4–51  |

| SN54ABT32952        | SN74ABT32952                | . 4–57  |

| Futurebus+/Bus Trar | sceiver Logic (FB+/BTL)     |         |

|                     | SN74FB1650                  | . 7–3   |

| SN54FB2031          | SN74FB2031                  | . 7–9   |

| SN54FB2032          | SN74FB2032                  | . 7–15  |

|                     | SN74FB2033                  | . 7–23  |

| SN54FB2040          | SN74FB2040                  | . 7–33  |

|                     | SN74FB2041                  | . 7–39  |

| Low-Voltage Technol |                             |         |

| SN54LVT125          | SN74LVT125                  | . 9–3   |

| SN54LVT240          | SN74LVT240                  | . 9–9   |

| SN54LVT244          | SN74LVT244                  | . 9–15  |

| SN54LVT245          | SN74LVT245                  | . 9–21  |

| SN54LVT273          | SN74LVT273                  | . 9–27  |

| SN54LVT543          | SN74LVT543                  |         |

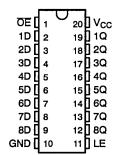

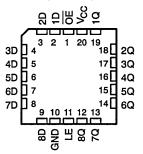

| SN54LVT573          | SN74LVT573                  | . 9–41  |

| SN54LVT574          | SN74LVT574                  | . 9–47  |

| SN54LVT646          | SN74LVT646                  |         |

| SN54LVT652          | SN74LVT652                  | . 9-63  |

| SN54LVT2952         | SN74LVT2952                 |         |

| SN54LVT16244        | SN74LVT16244                |         |

| SN54LVT16245        | SN74LVT16245                |         |

| SN54LVT16373        | SN74LVT16373                |         |

| SN54LVT16374        | SN74LVT16374                |         |

| SN54LVT16500        | SN74LVT16500                |         |

| SN54LVT16501        | SN74LVT16501                |         |

| SN54LVT16543        | SN74LVT16543                | . 10-43 |

| SN54LVT16646        | SN74LVT16646                | . 10-49 |

| SN54LVT16652        | SN74LVT16652                | . 10–57 |

| CNEALVETTOCEO       | CNIZALVETACOCO              | 40.00   |

### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

### **OPERATING CONDITIONS AND CHARACTERISTICS (IN SEQUENCE BY LETTER SYMBOLS)**

C<sub>i</sub> Input capacitance

The internal capacitance at an input of the device.

C<sub>o</sub> Output capacitance

The internal capacitance at an output of the device.

C<sub>pd</sub> Power dissipation capacitance

Used to determine the no-load dynamic power dissipation per logic function (see individual circuit pages):  $P_D = C_{od} V_{CC}^2 f + I_{CC} V_{CC}$ .

f<sub>max</sub> Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

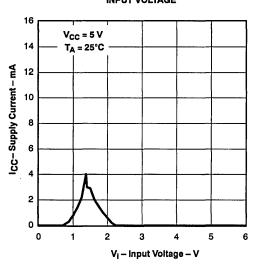

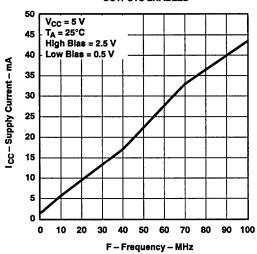

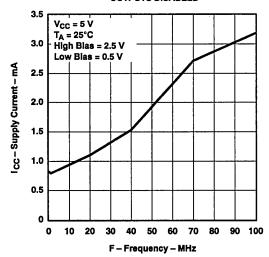

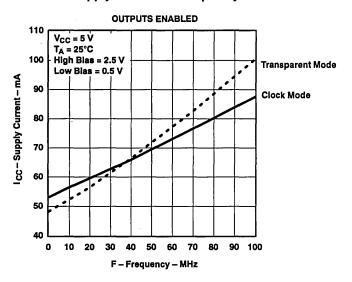

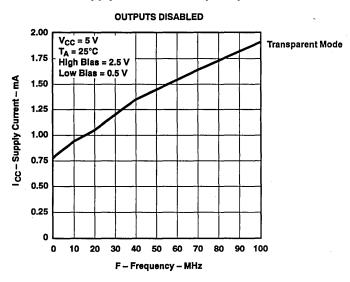

I<sub>CC</sub> Supply current

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit.

ΔI<sub>CC</sub> Supply current change

The increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or  $V_{CC}$ .

I<sub>CEX</sub> Output high leakage current

The maximum leakage current into the collector of the pulldown output transistor when the output is high and the output forcing condition  $V_{\rm O} = 5.5$  V.

I<sub>IH</sub> High-level input current

The current into\* an input when a high-level voltage is applied to that input.

I<sub>IL</sub> Low-level input current

The current into\* an input when a low-level voltage is applied to that input.

Input/output power-off leakage current

The maximum leakage current into/out of the input/output transistors when forcing the input/output to 4.5 V and  $V_{CC} = 0 \text{ V}$ .

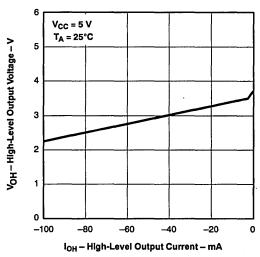

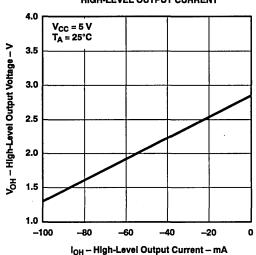

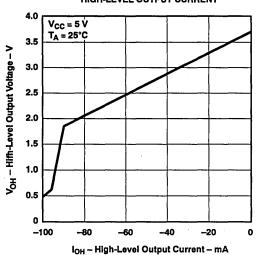

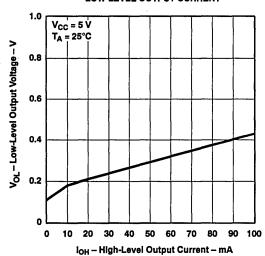

I<sub>OH</sub> High-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a high level at the output.

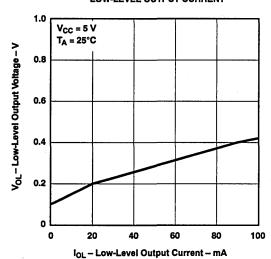

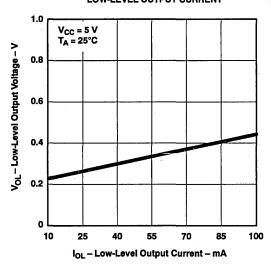

I<sub>OL</sub> Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a low level at the output.

I<sub>OZ</sub> Off-state (high-impedance-state) output current (of a 3-state output)

The current flowing into\* an output having 3-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output.

<sup>\*</sup>Current out of a terminal is given as a negative value.

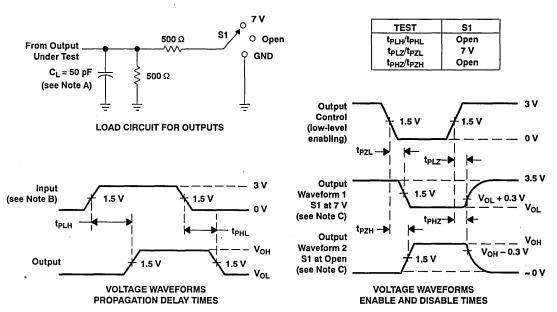

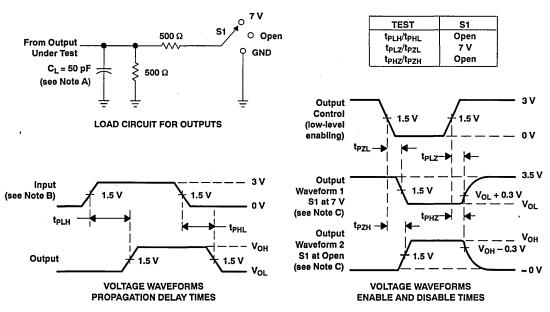

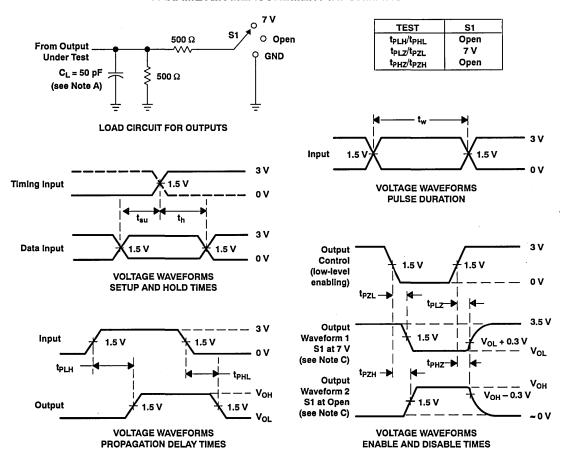

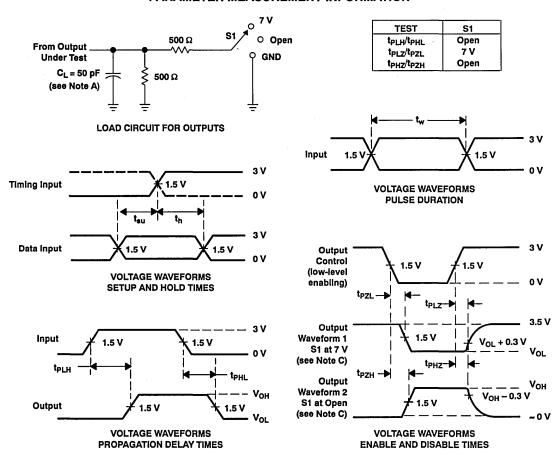

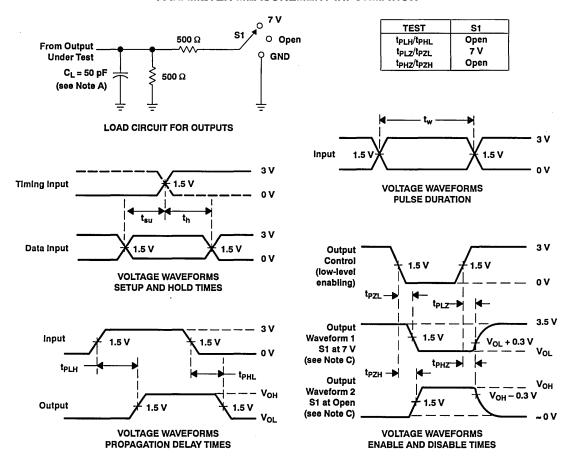

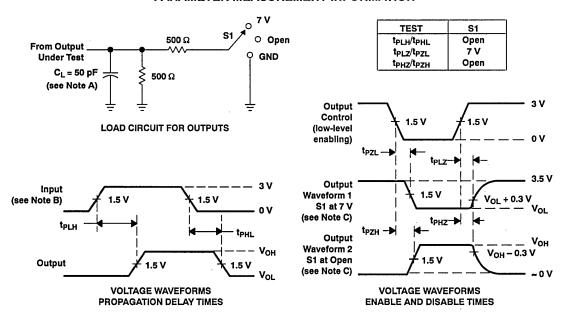

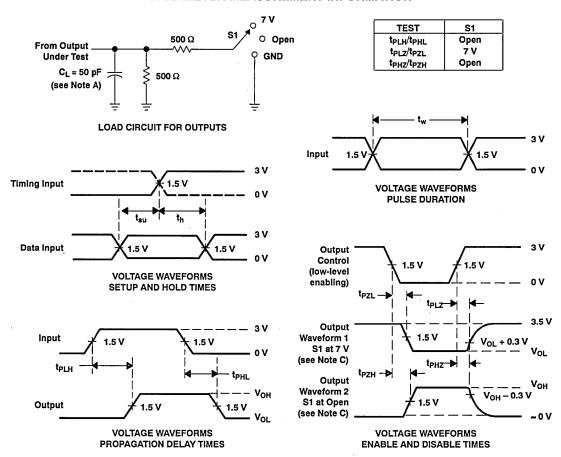

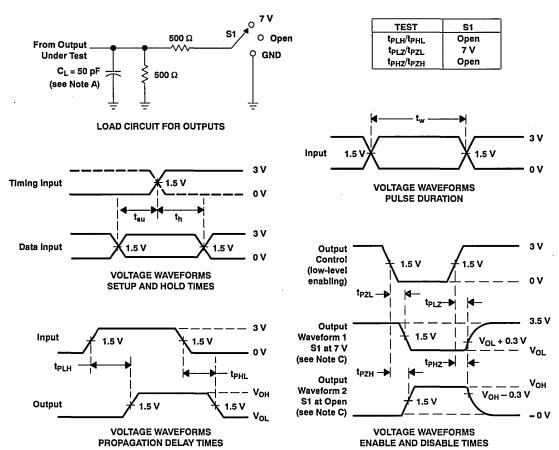

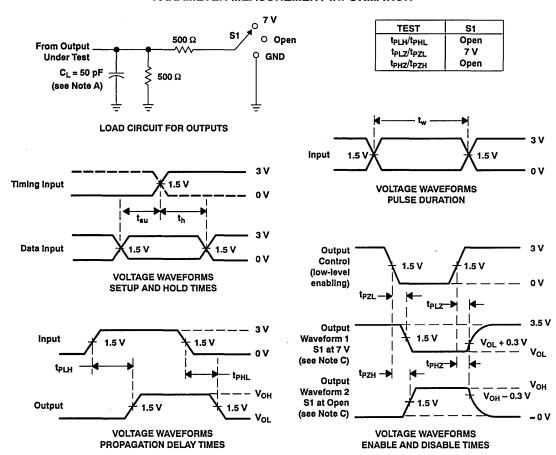

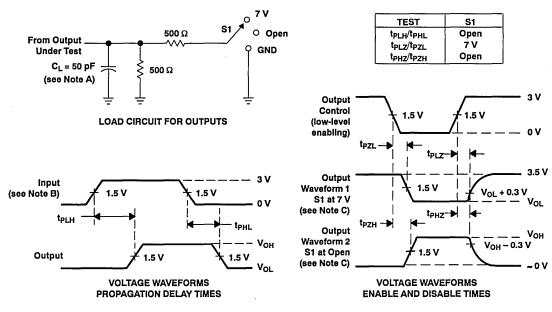

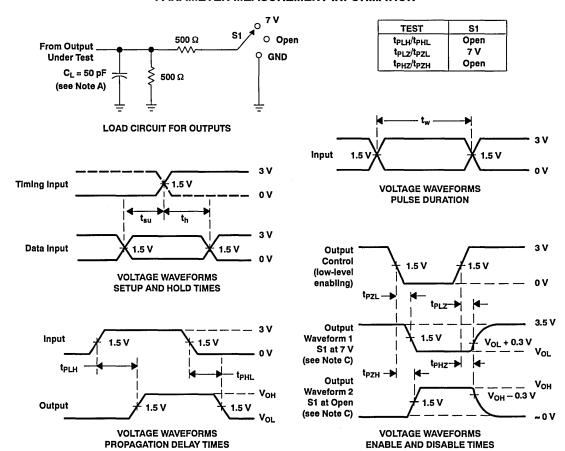

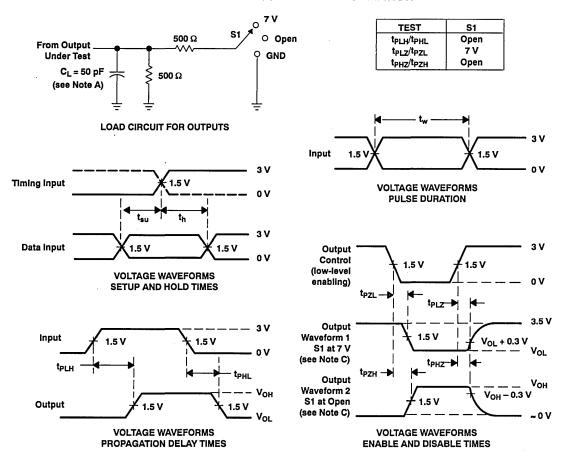

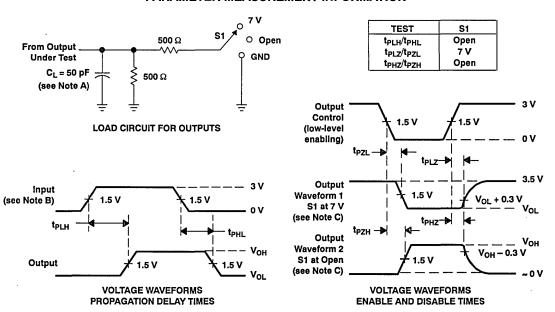

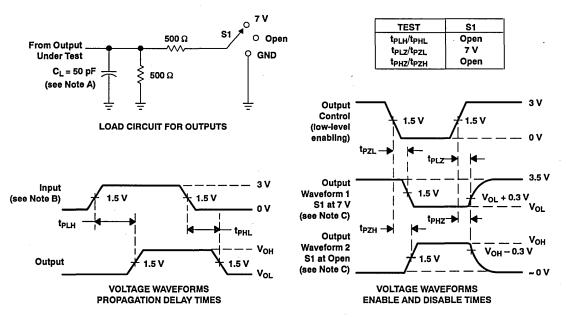

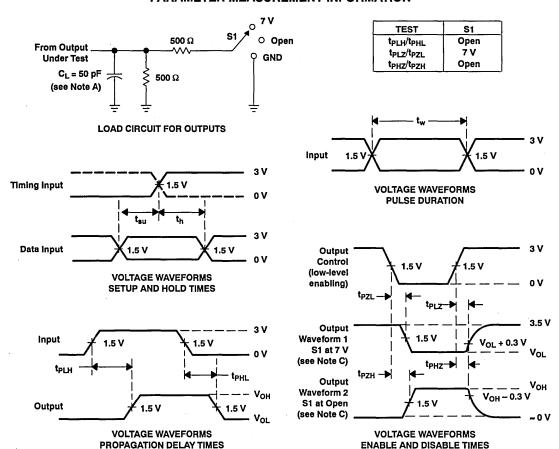

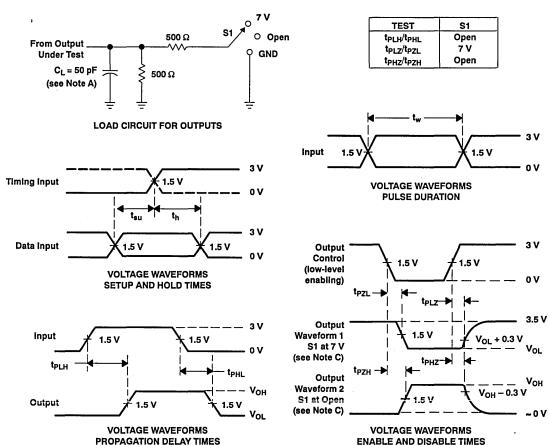

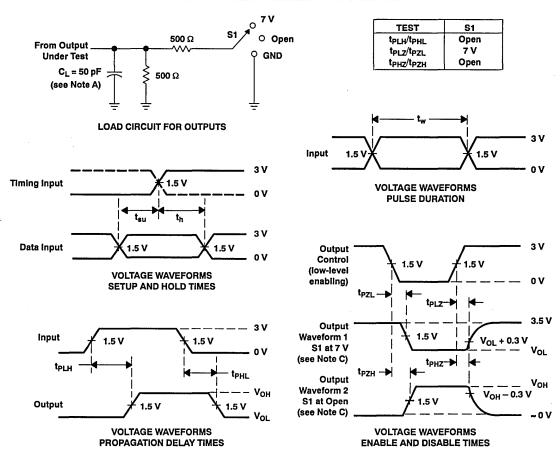

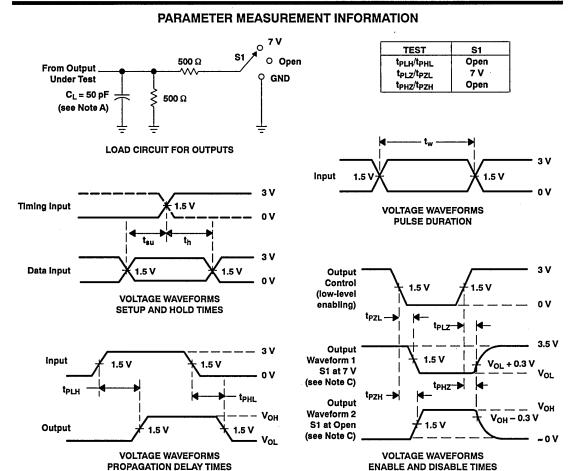

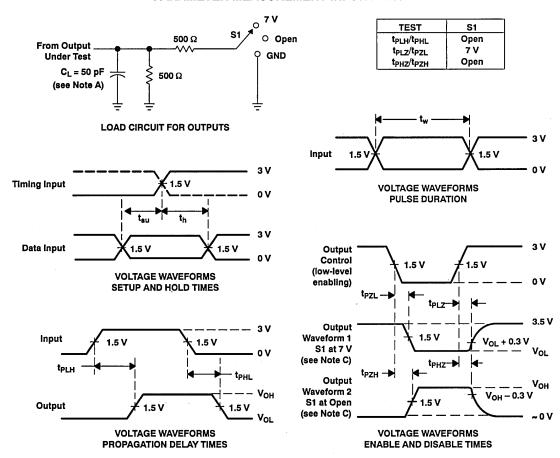

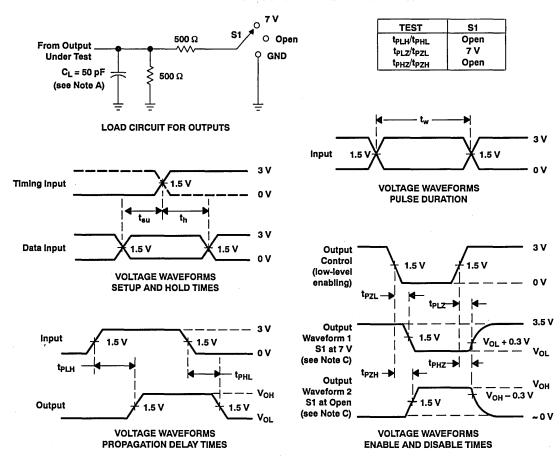

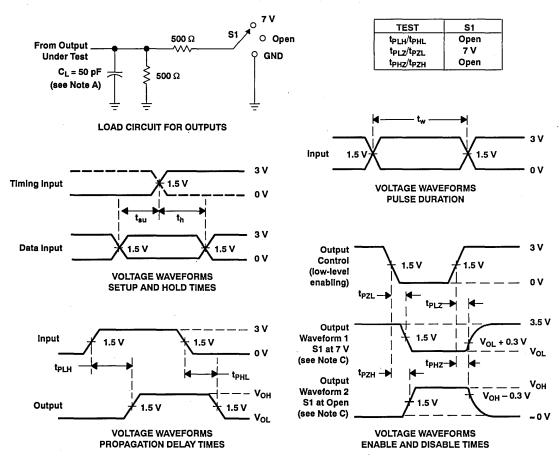

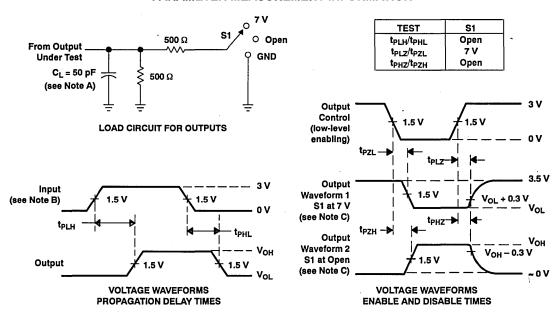

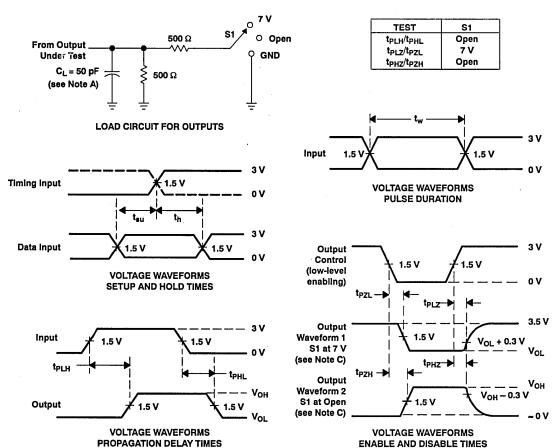

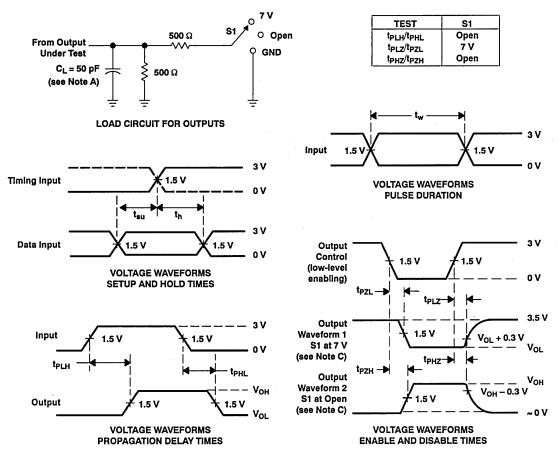

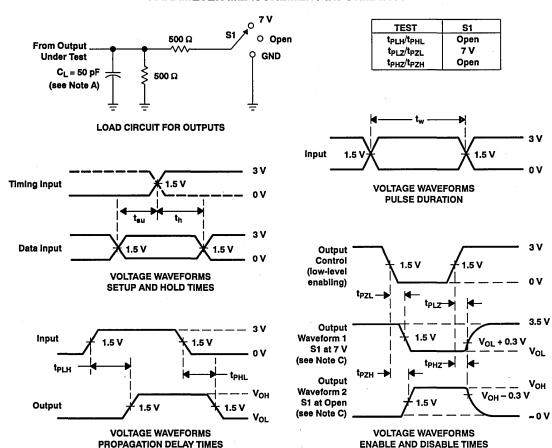

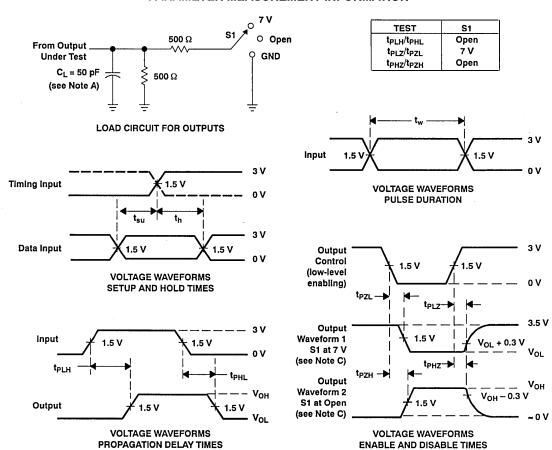

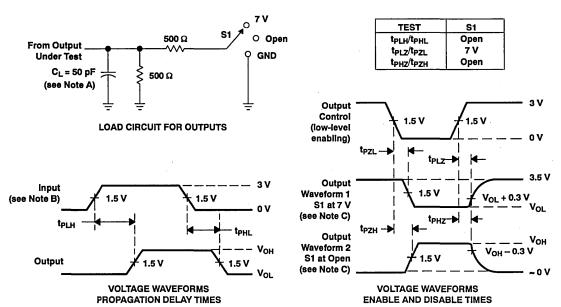

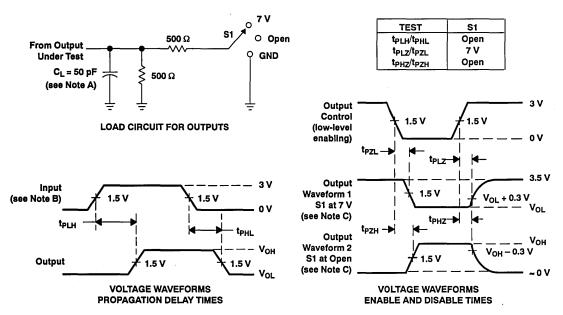

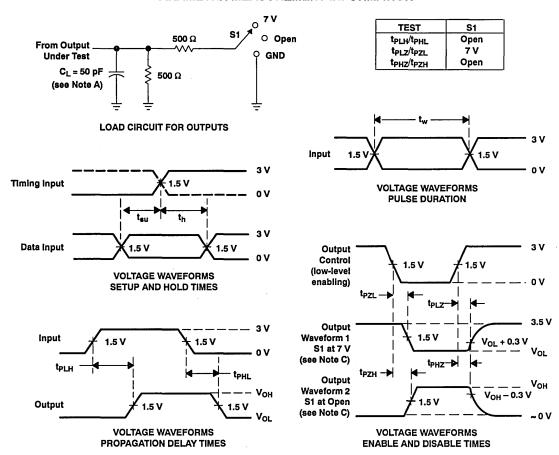

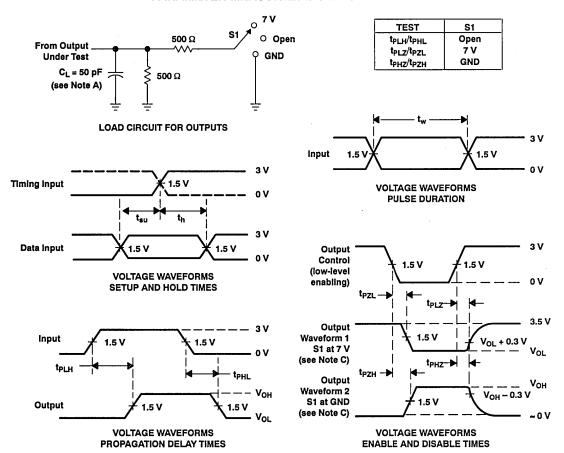

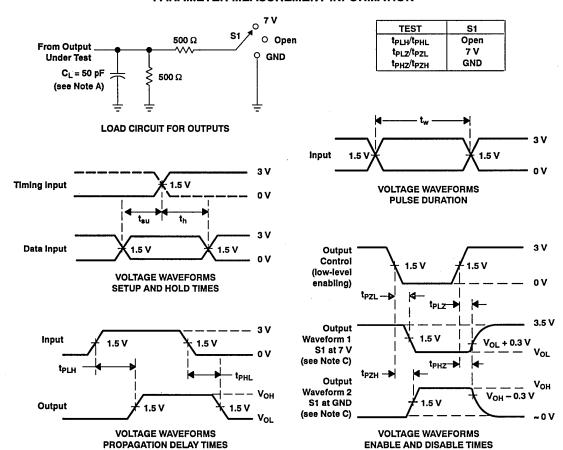

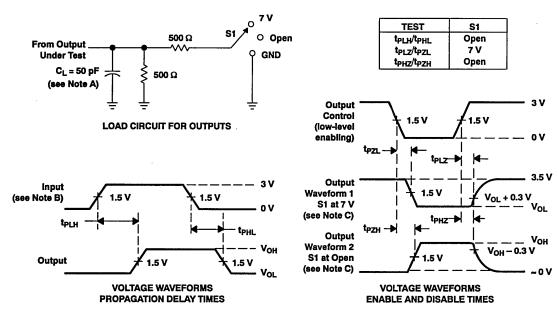

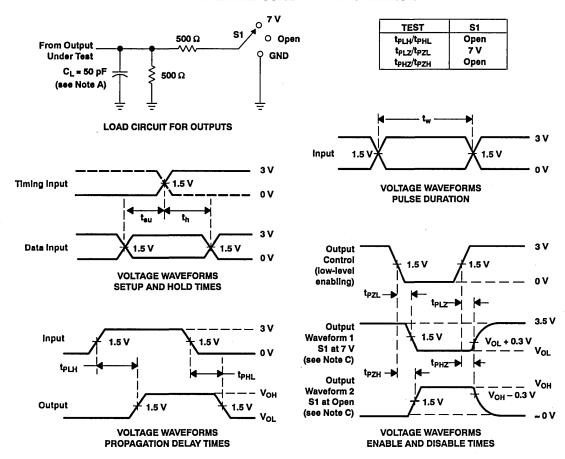

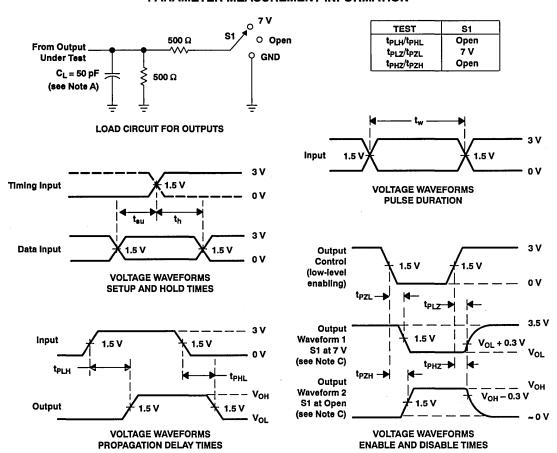

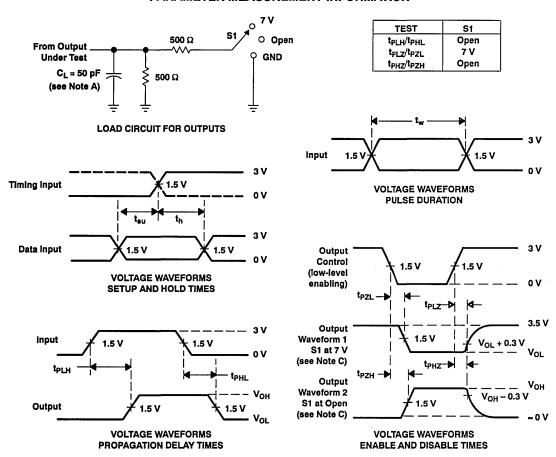

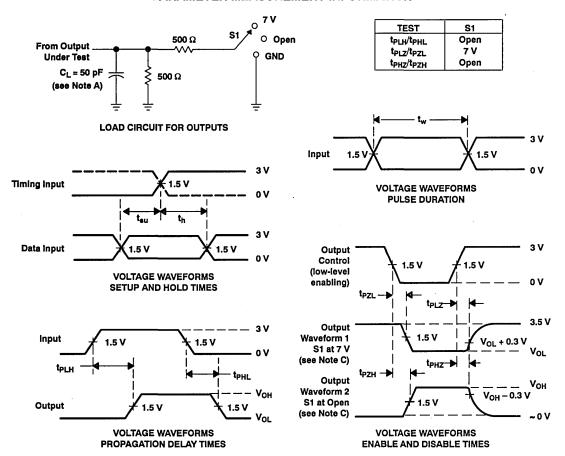

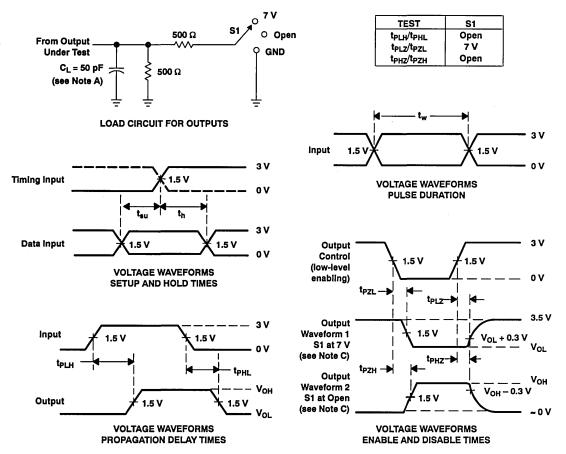

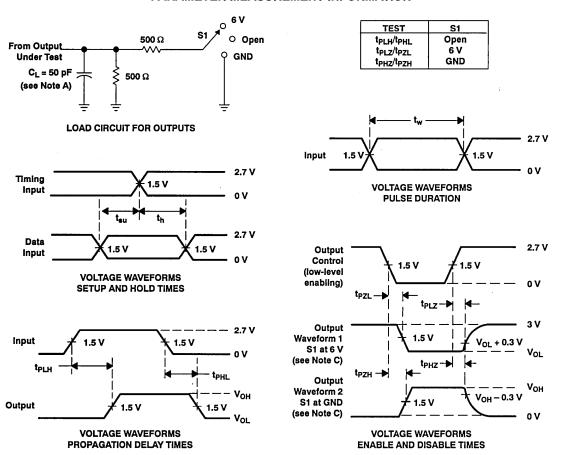

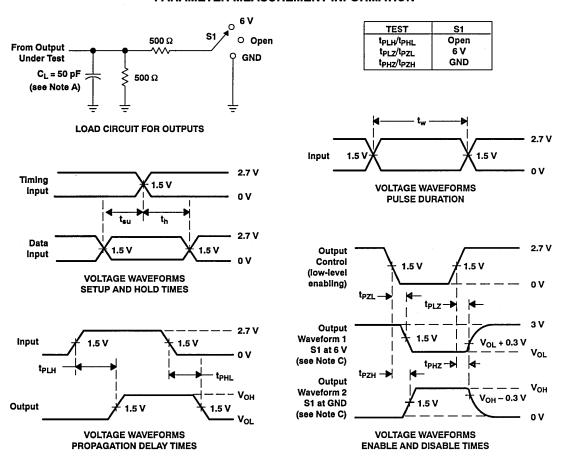

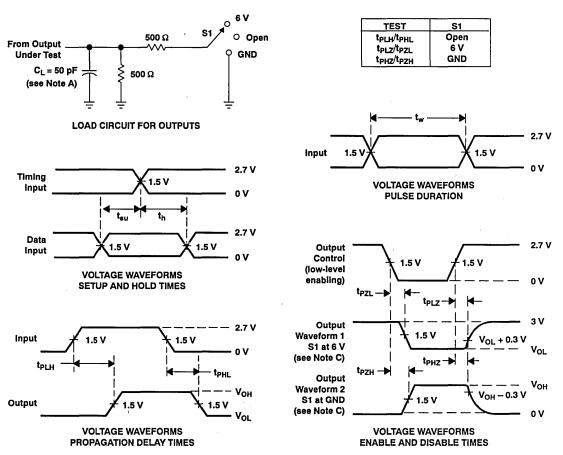

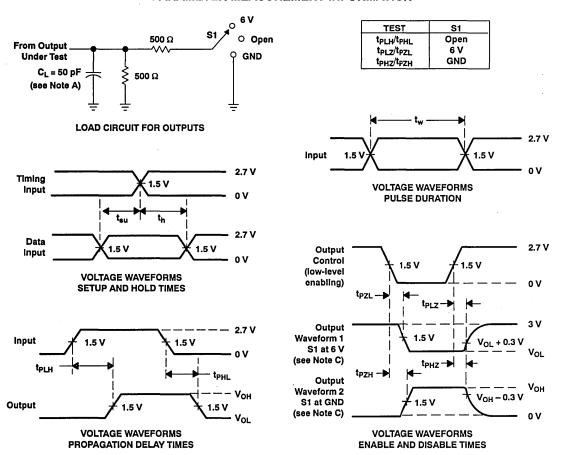

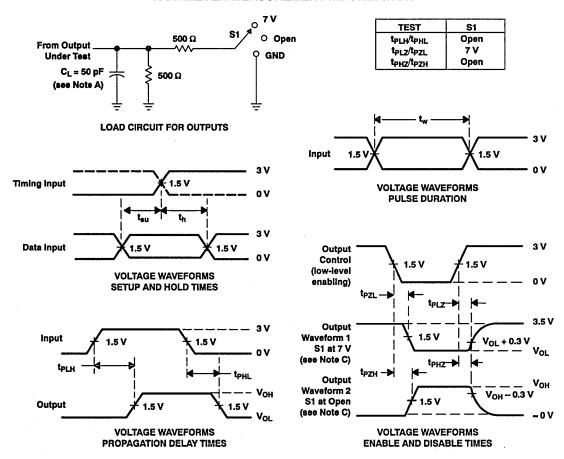

### t<sub>a</sub> Access time

The time interval between the application of a specified input pulse and the availability of valid signals at an output.

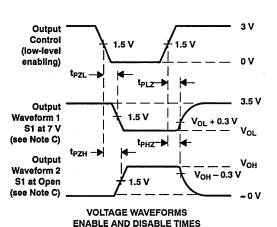

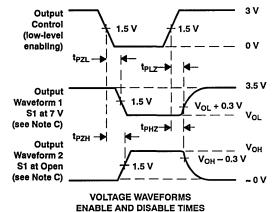

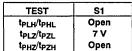

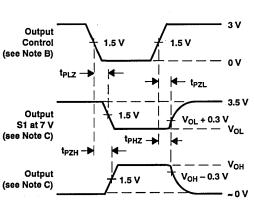

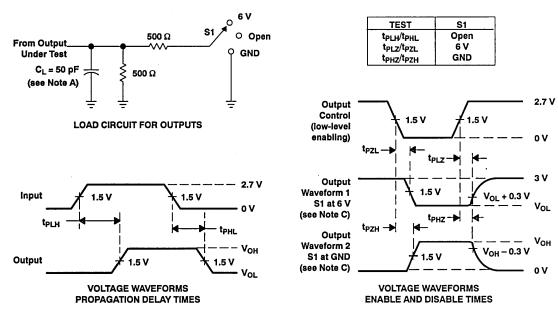

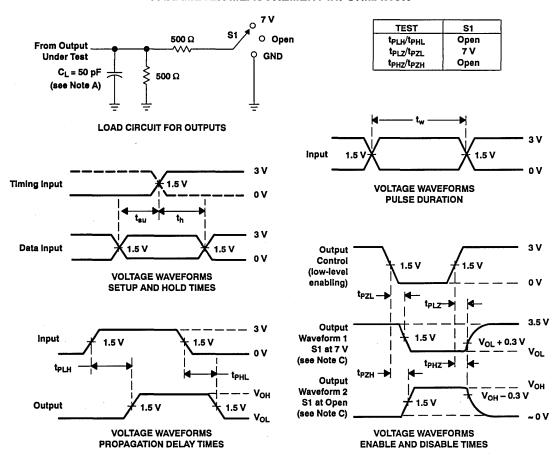

### t<sub>dis</sub> Disable time (of a 3-state or open-collector output)

The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from either of the defined active levels (high or low) to a high-impedance (off) state.

NOTE: For 3-state outputs,  $t_{dis} = t_{PHZ}$  or  $t_{PLZ}$ . Open-collector outputs will change only if they are low at the time of disabling so  $t_{dis} = t_{PLH}$ .

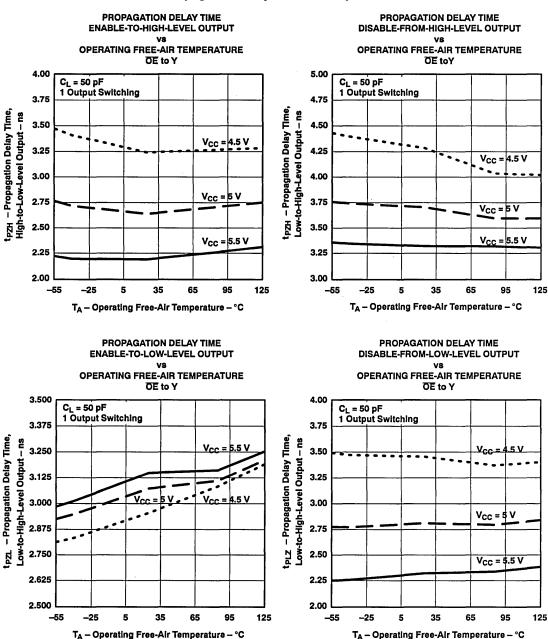

### t<sub>en</sub> Enable time (of a 3-state or open-collector output)

The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from a high-impedance (off) state to either of the defined active levels (high or low).

NOTE: In the case of memories, this is the access time from an enable input (e.g.,  $\overline{OE}$ ). For 3-state outputs,  $t_{en} = t_{PZH}$  or  $t_{PZL}$ . Open-collector outputs will change only if they are responding to data that would cause the output to go low so, for them  $t_{en} = t_{PHL}$ .

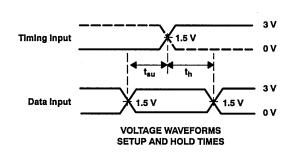

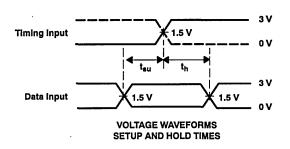

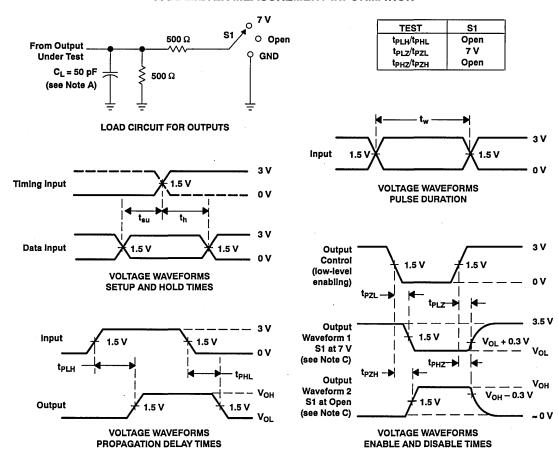

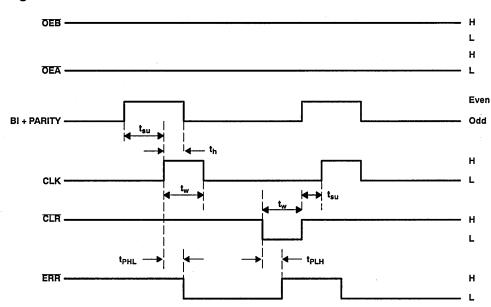

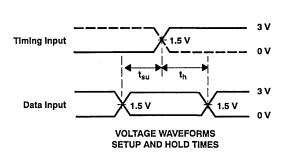

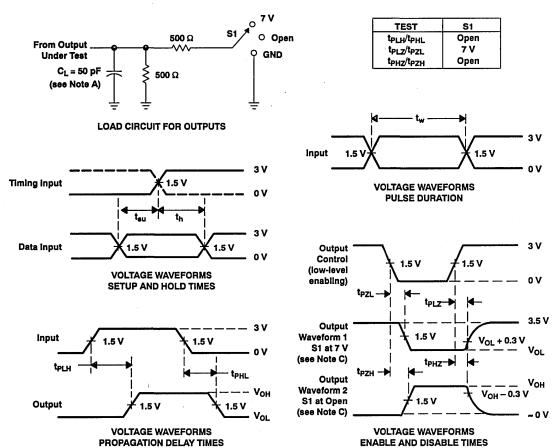

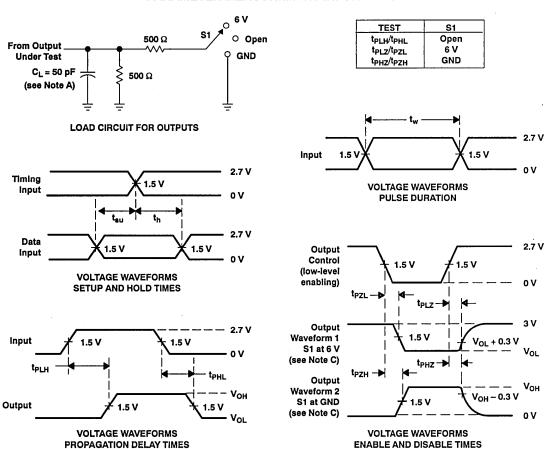

### th Hold time

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

NOTES: 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

2. The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is guaranteed.

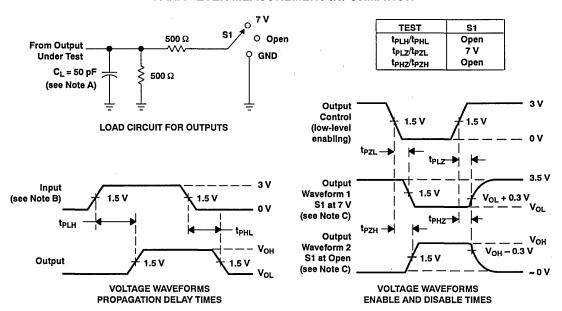

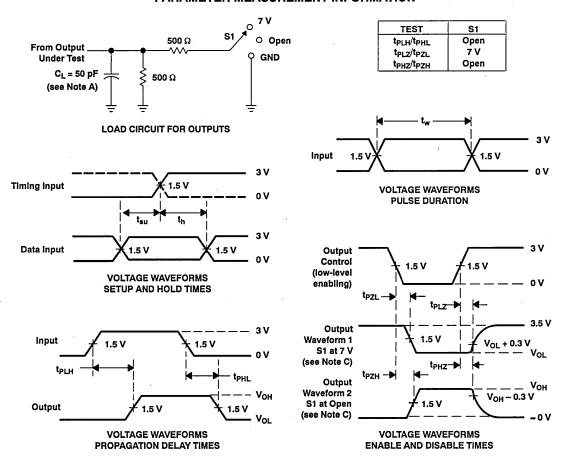

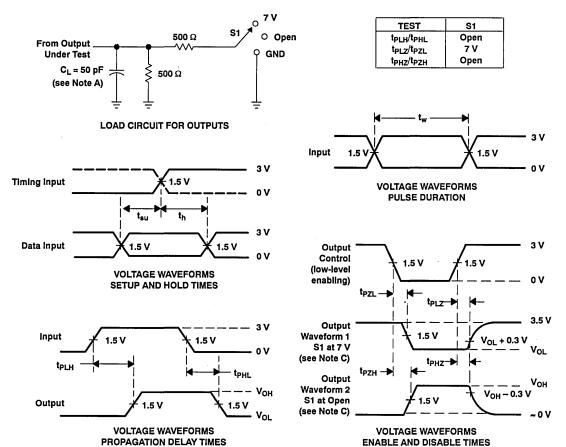

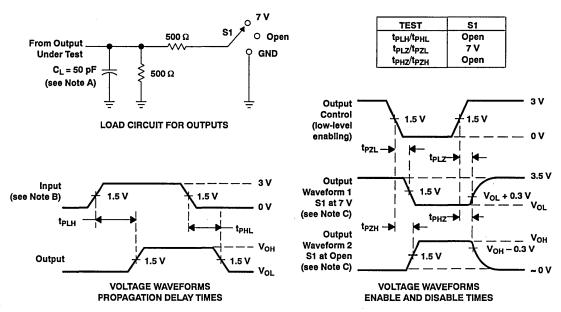

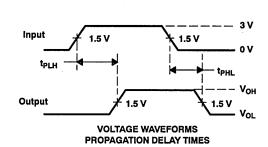

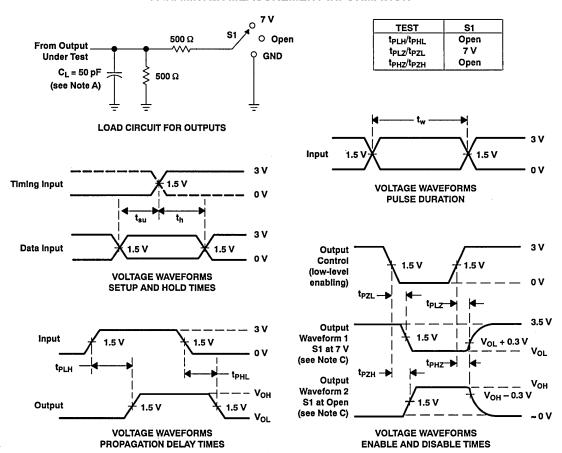

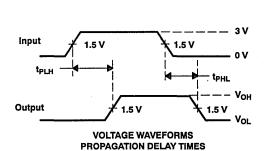

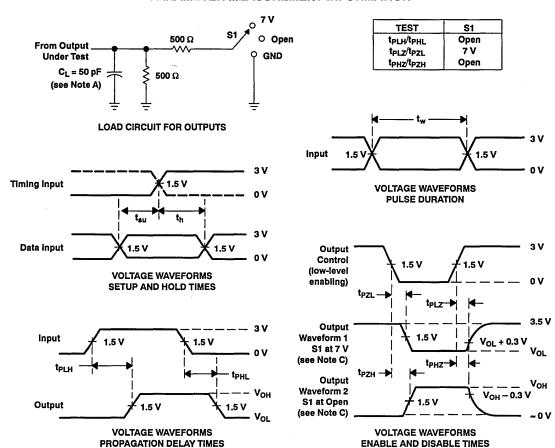

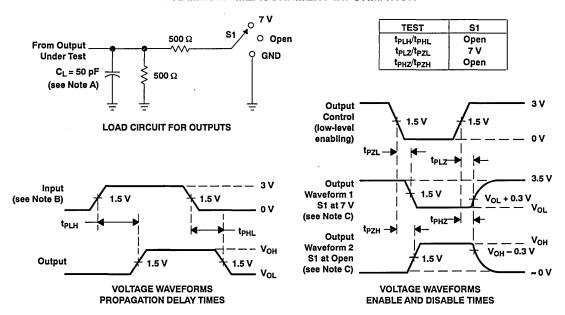

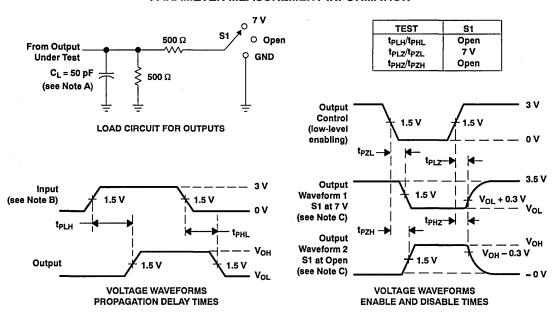

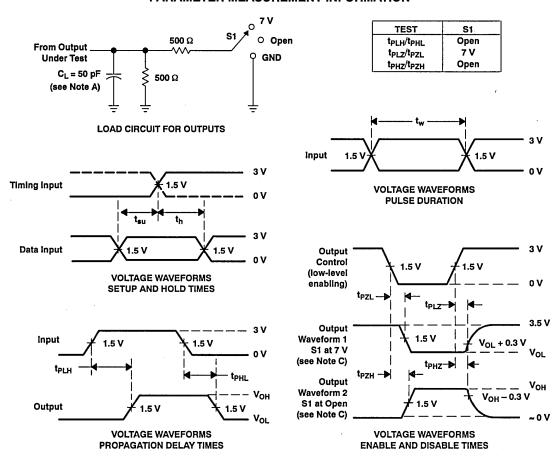

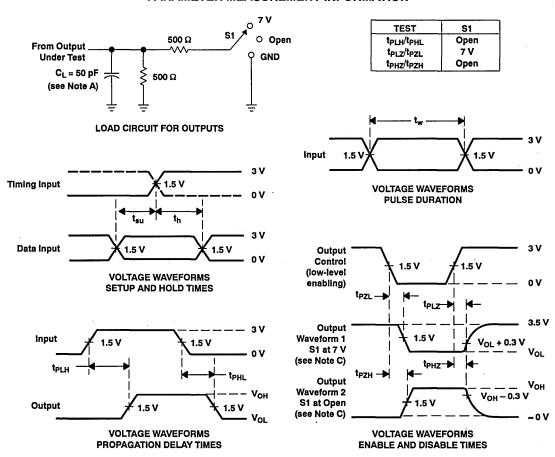

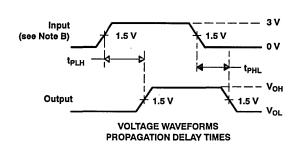

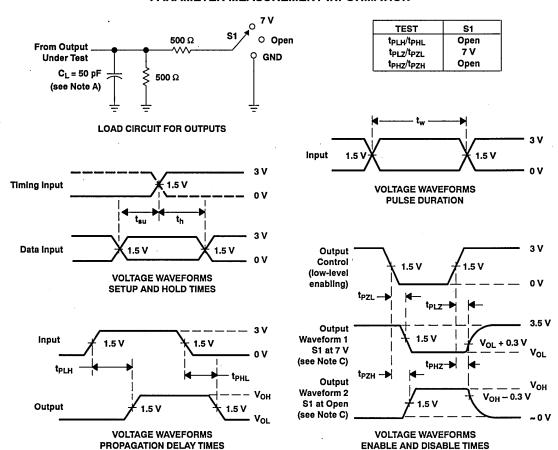

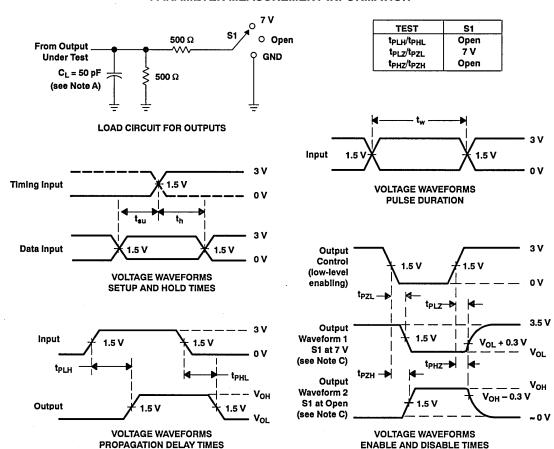

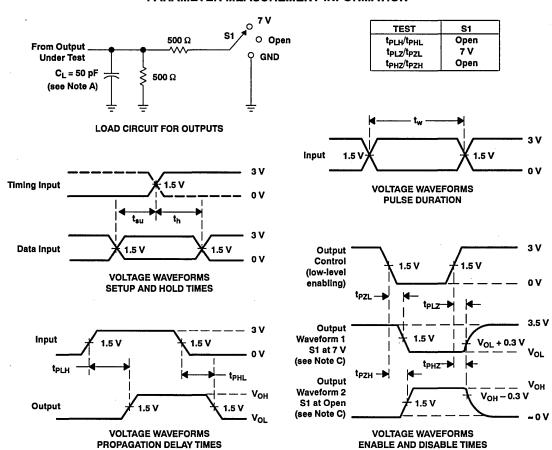

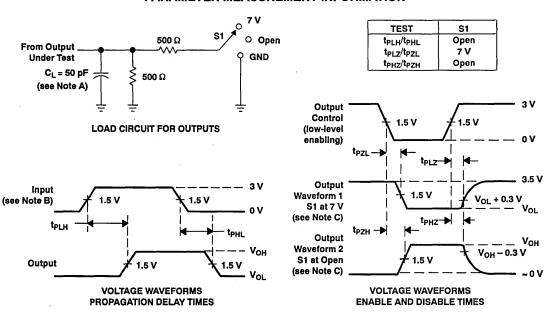

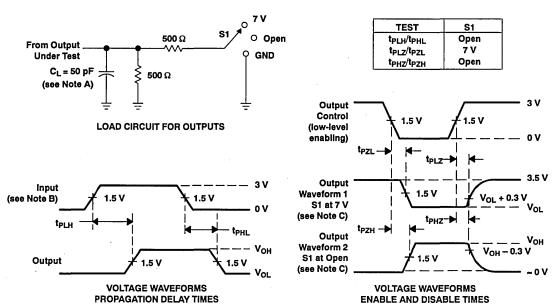

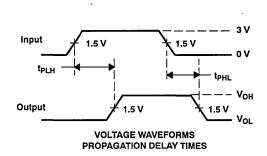

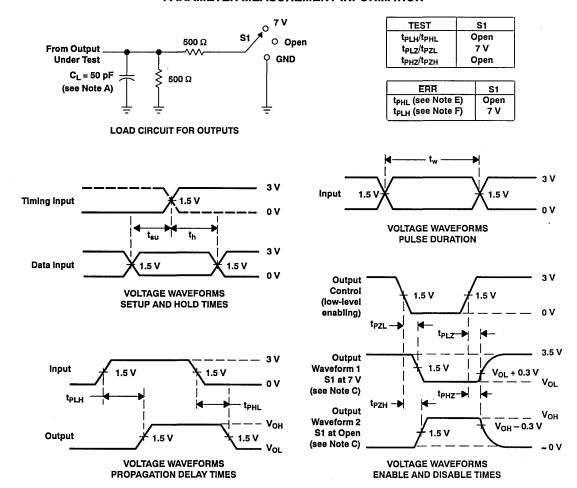

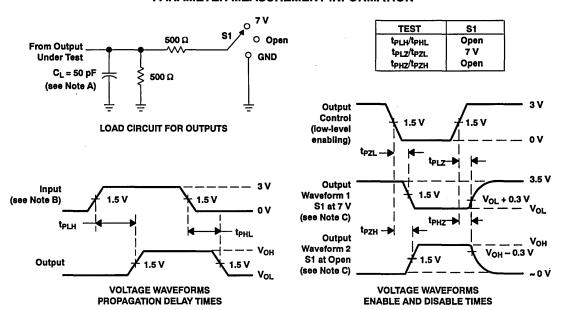

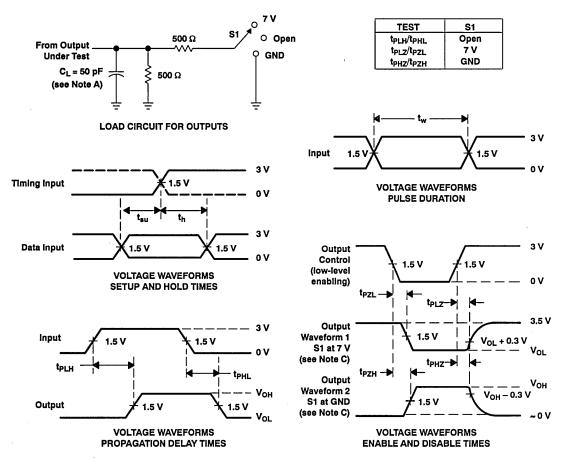

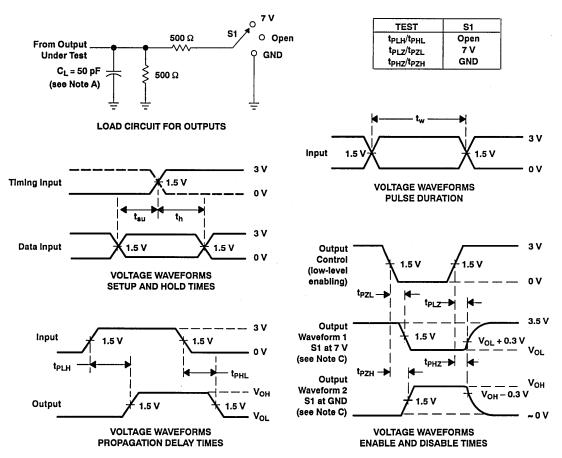

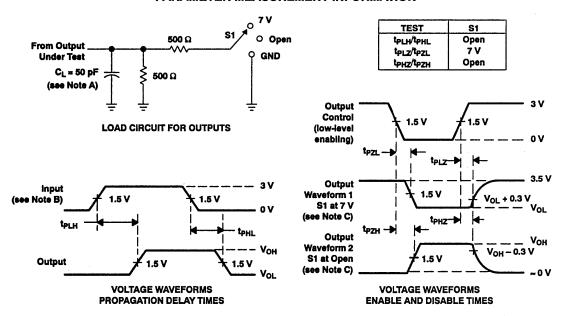

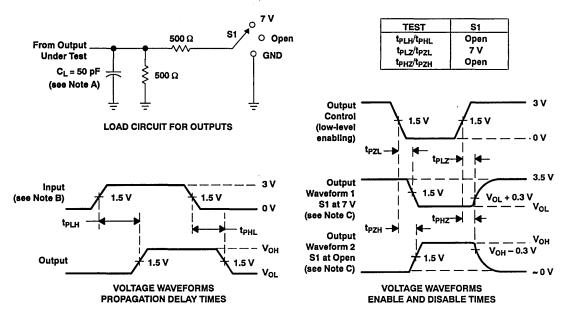

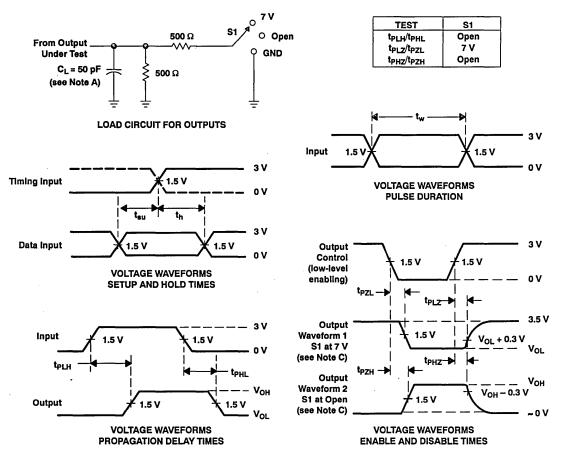

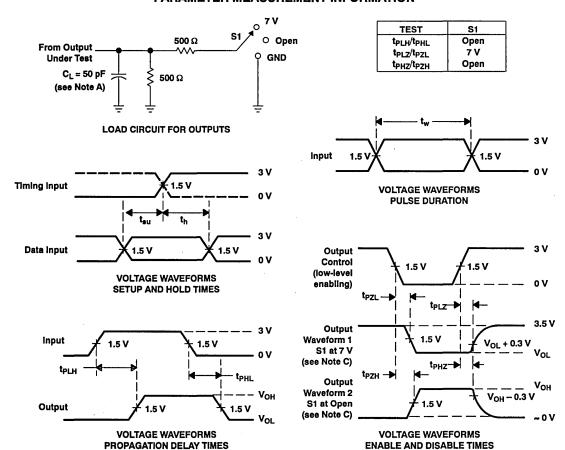

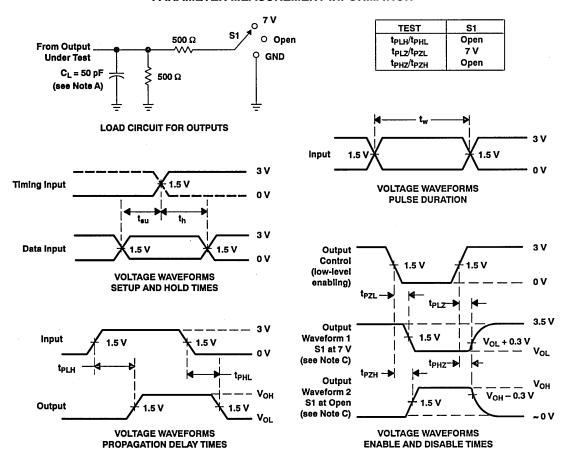

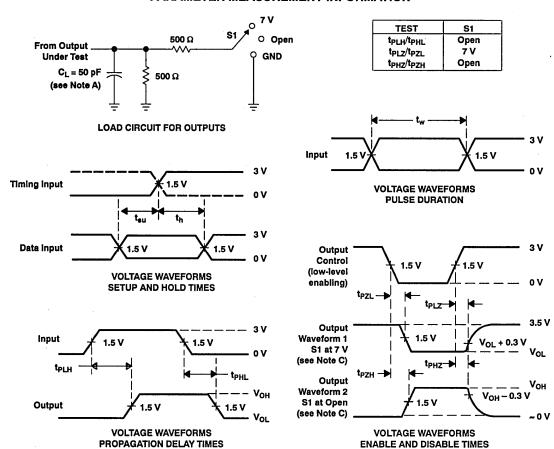

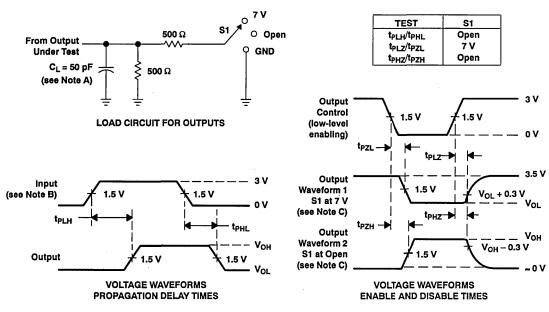

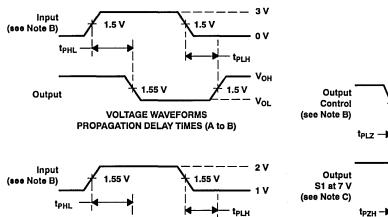

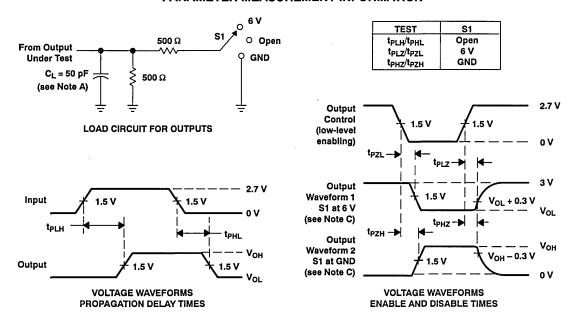

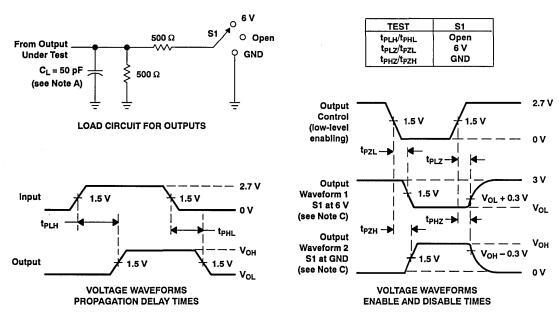

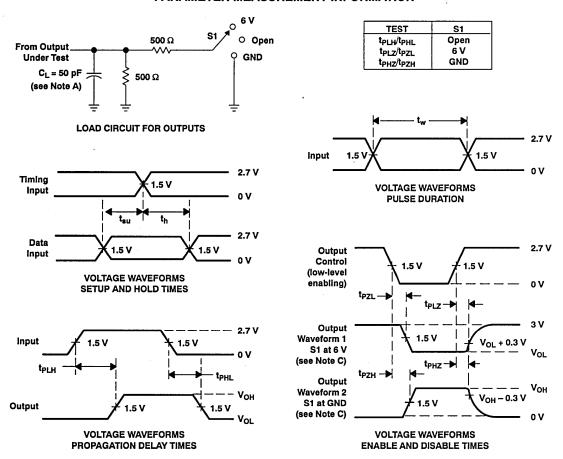

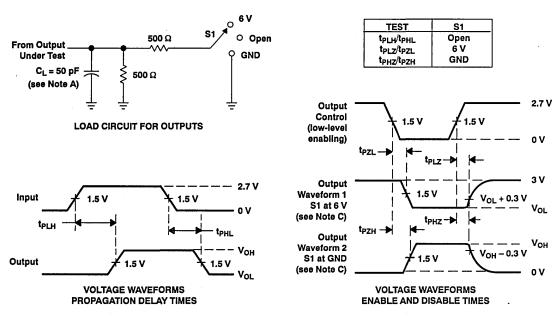

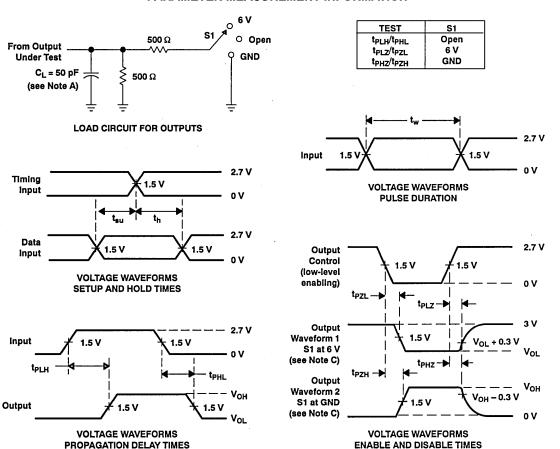

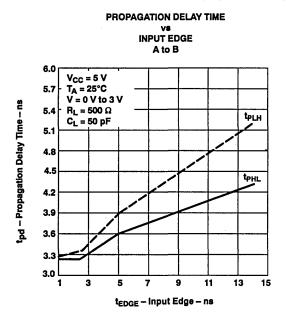

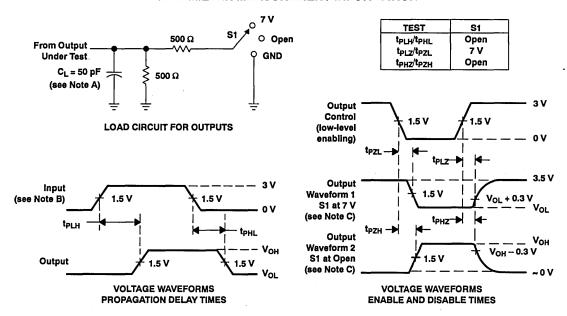

### t<sub>pd</sub> Propagation delay time

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level. ( $t_{pd} = t_{PHL}$  or  $t_{PLH}$ ).

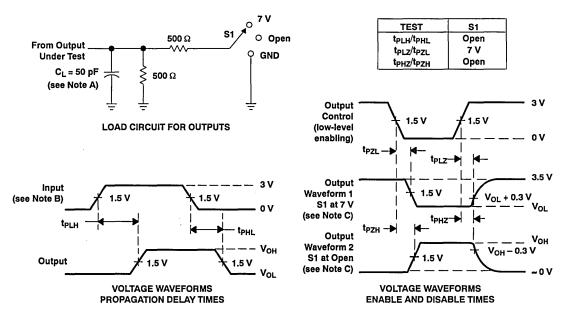

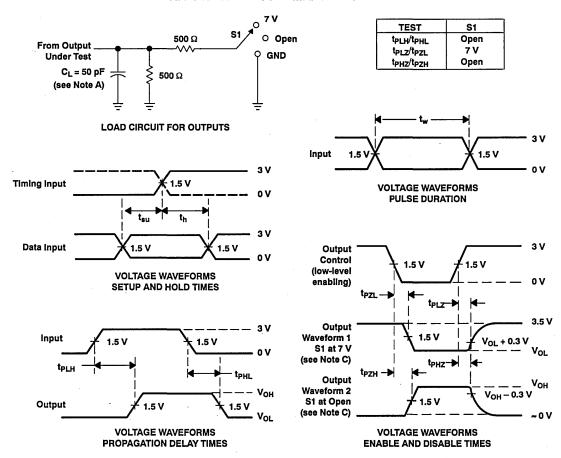

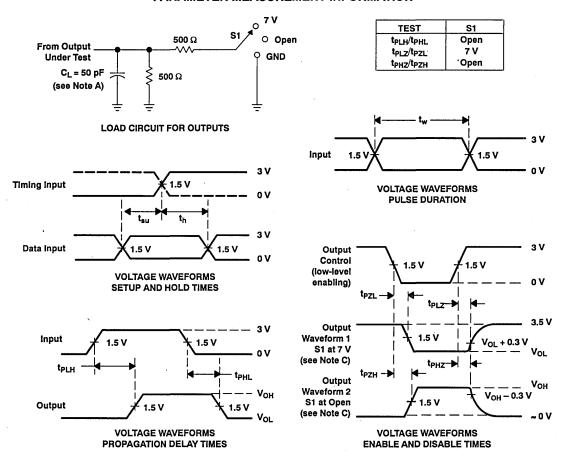

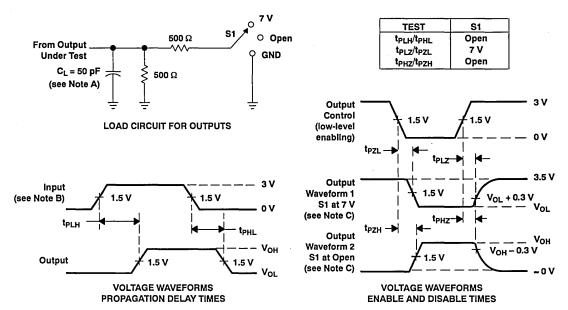

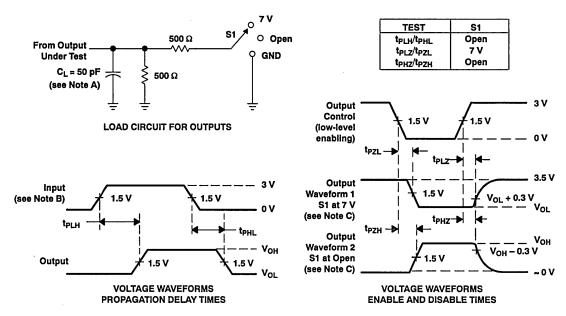

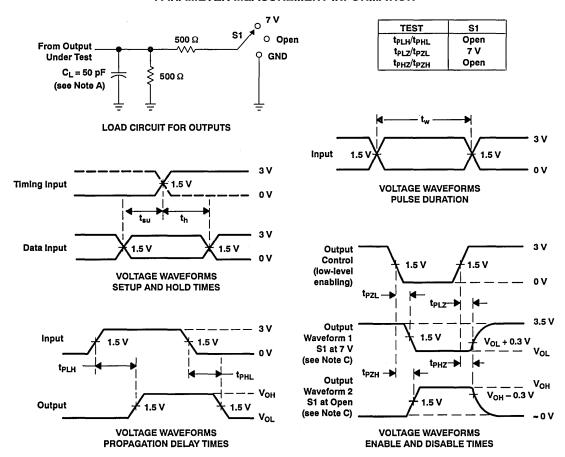

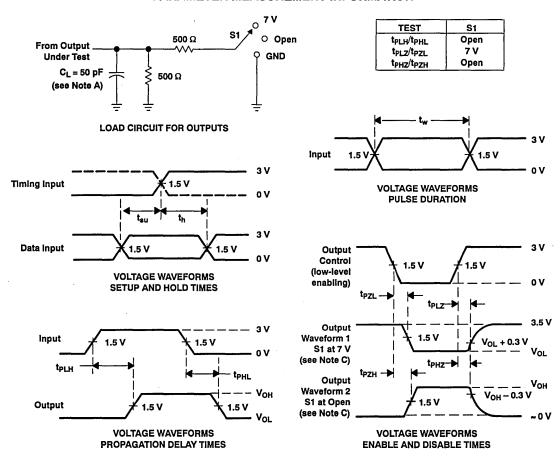

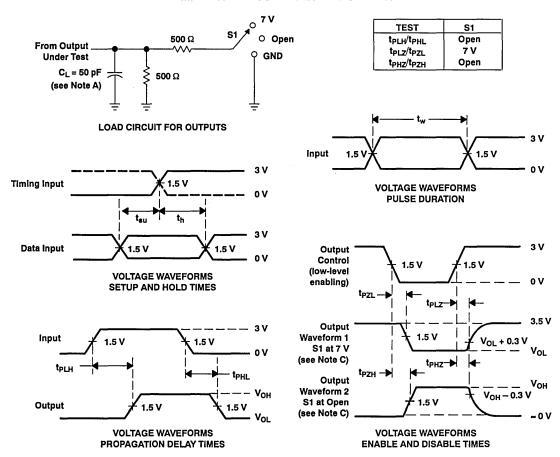

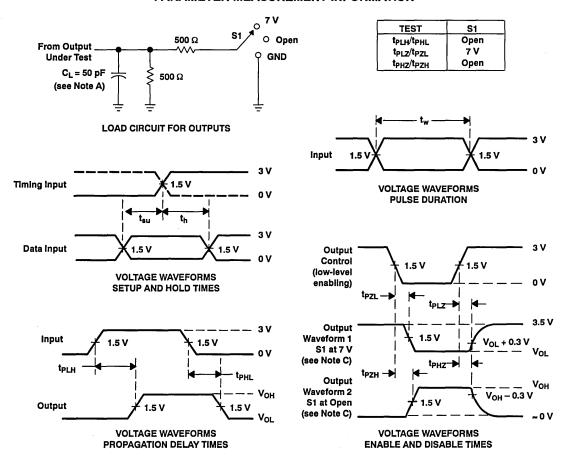

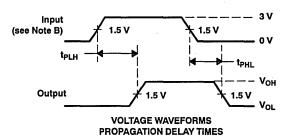

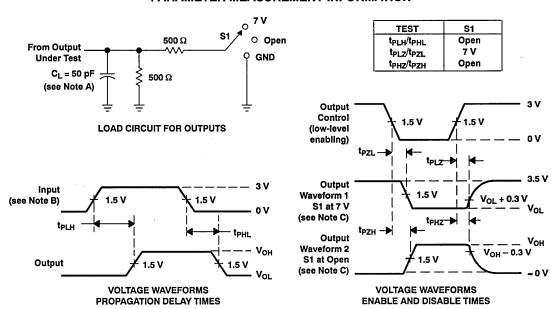

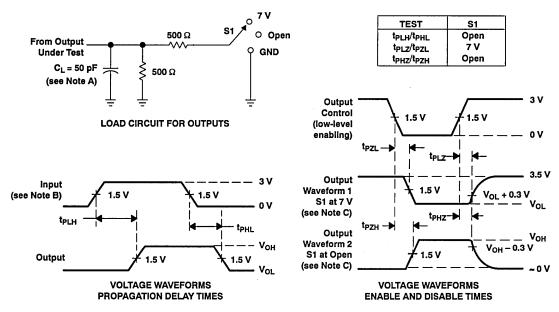

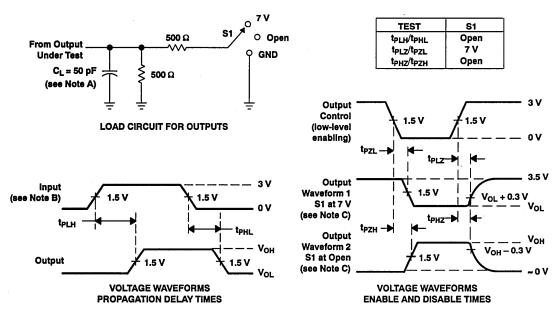

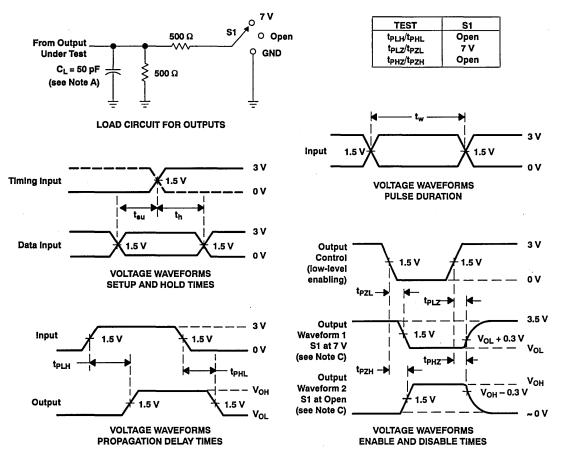

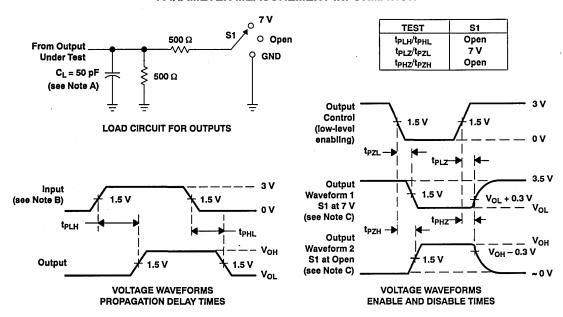

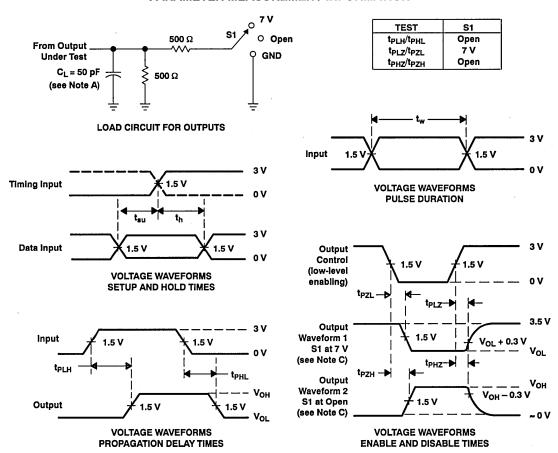

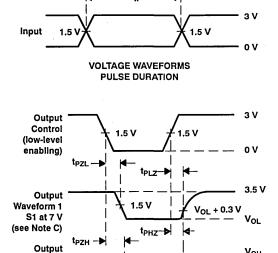

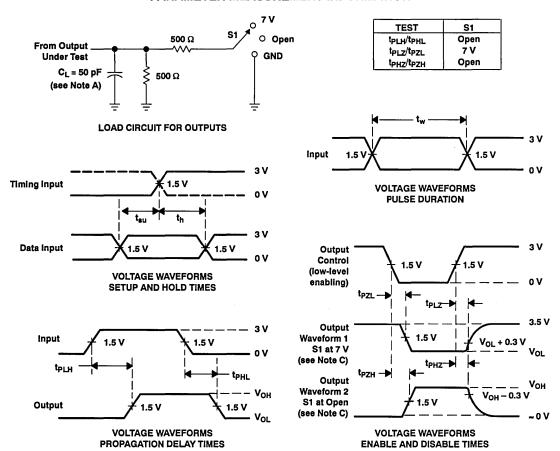

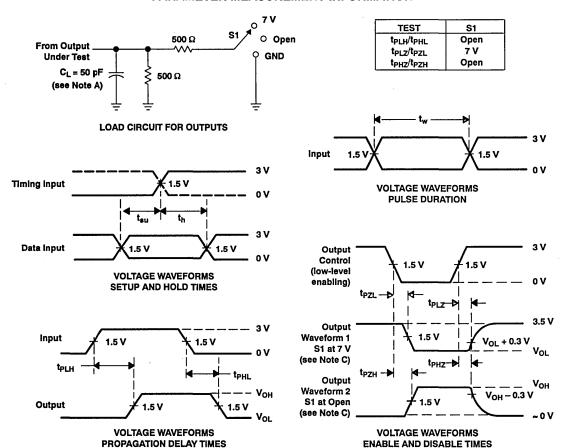

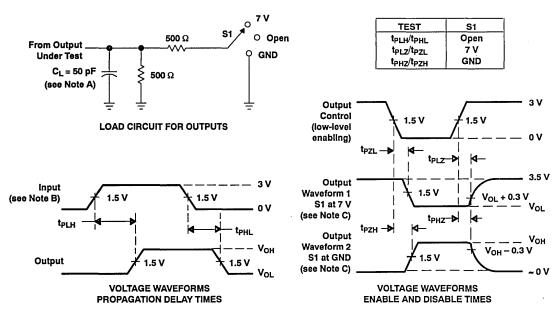

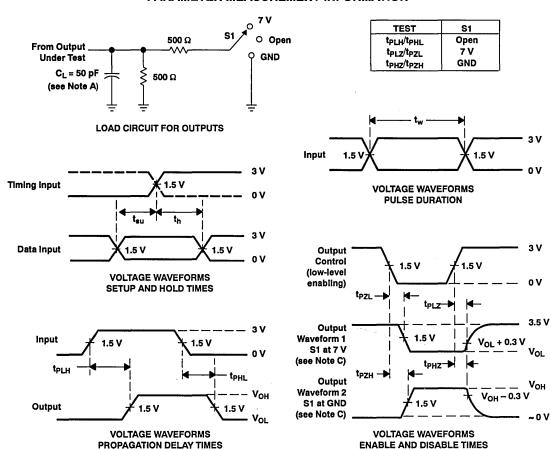

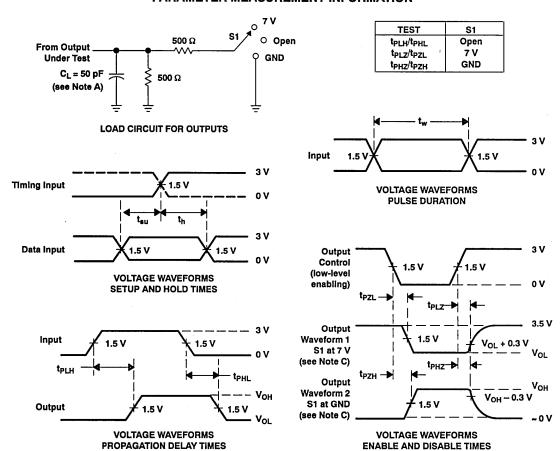

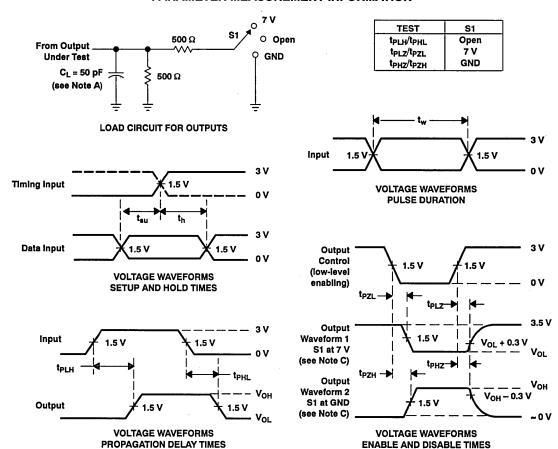

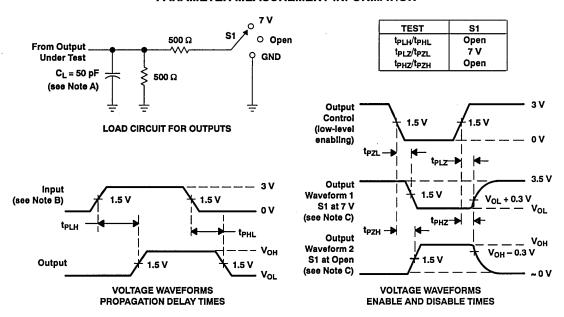

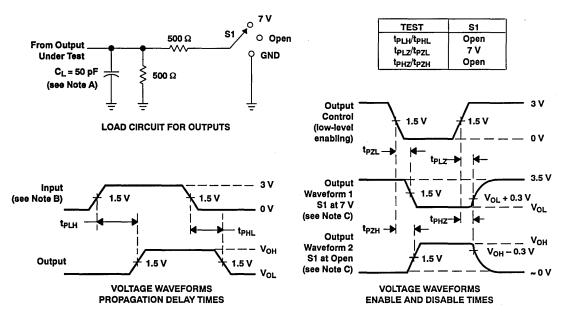

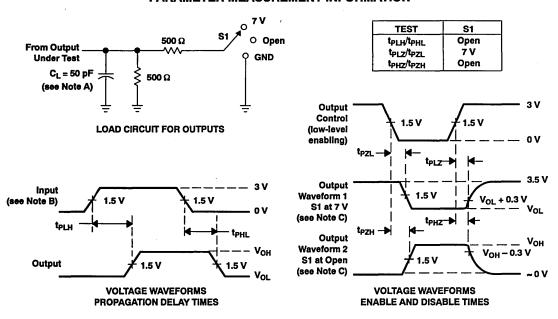

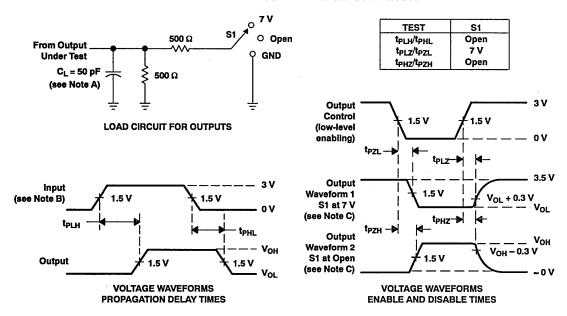

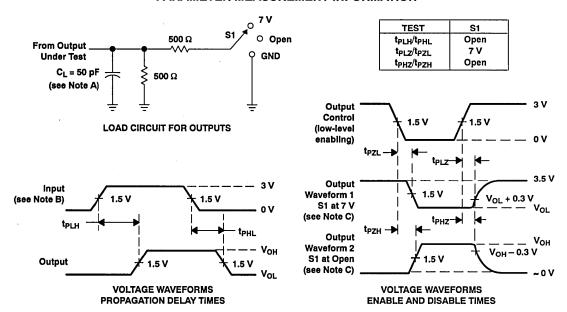

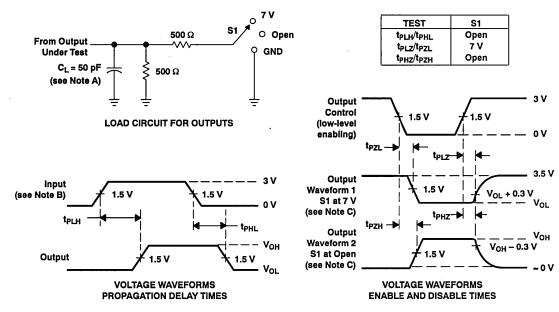

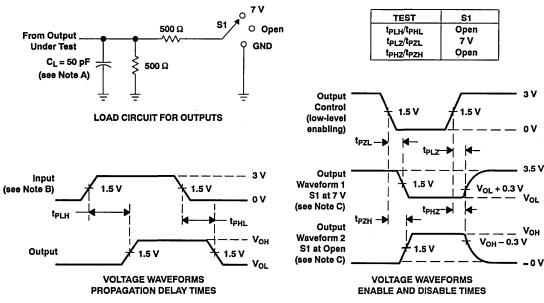

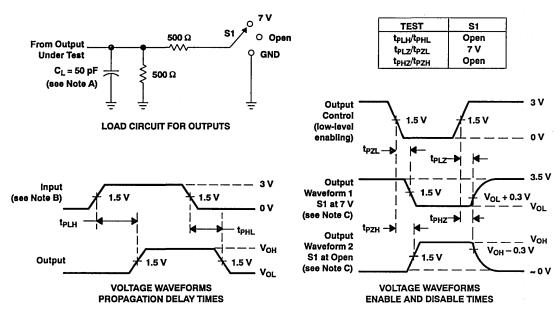

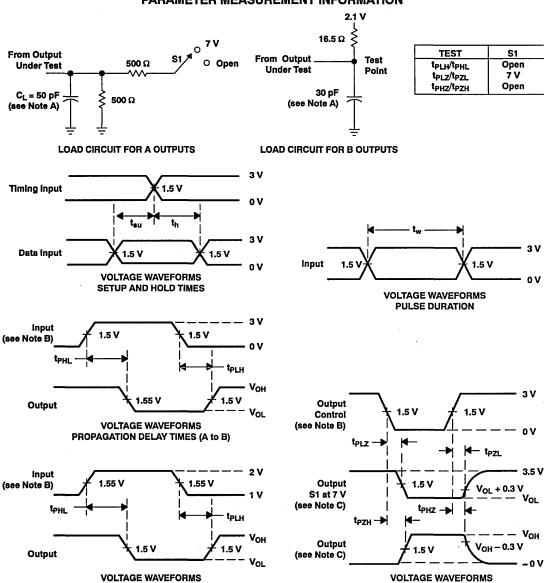

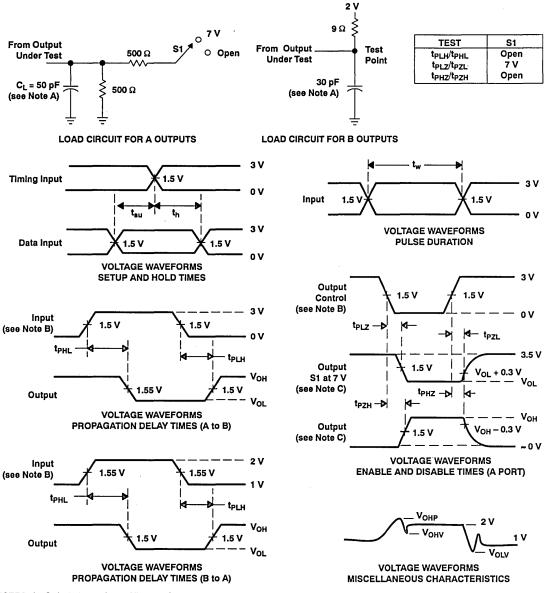

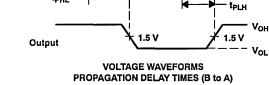

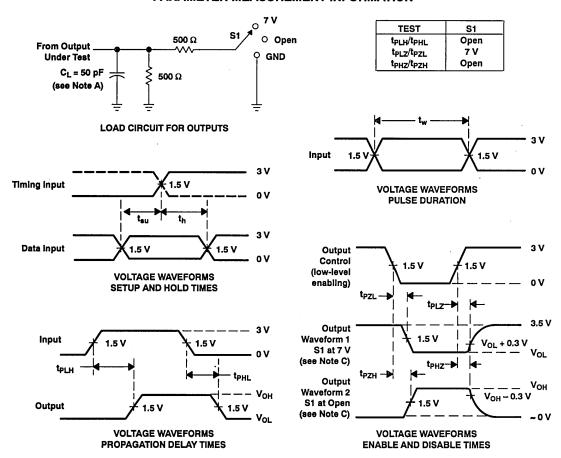

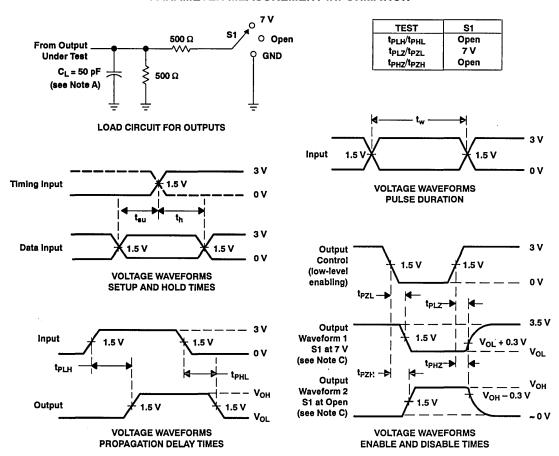

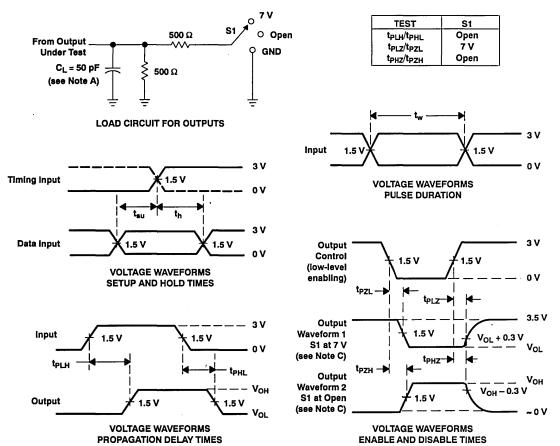

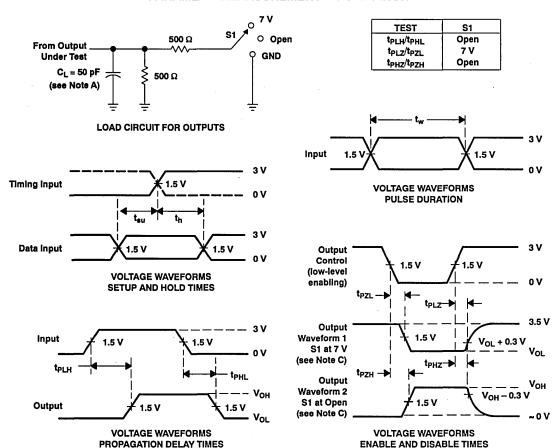

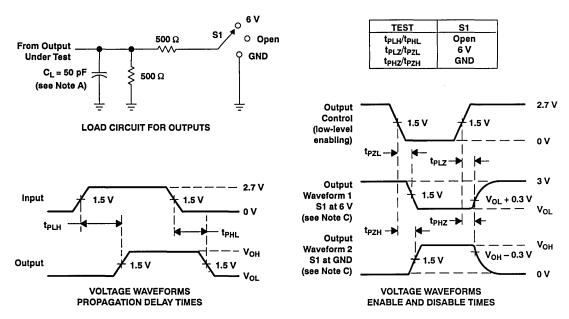

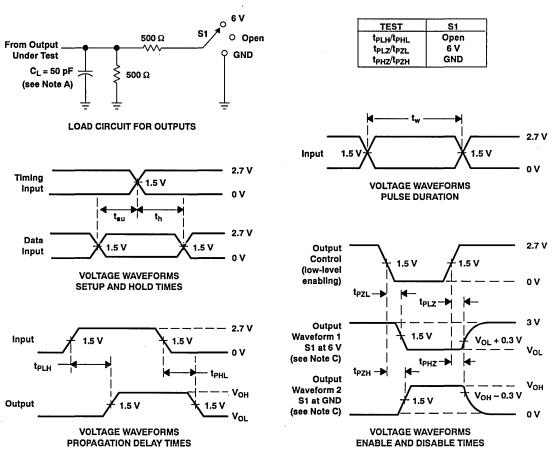

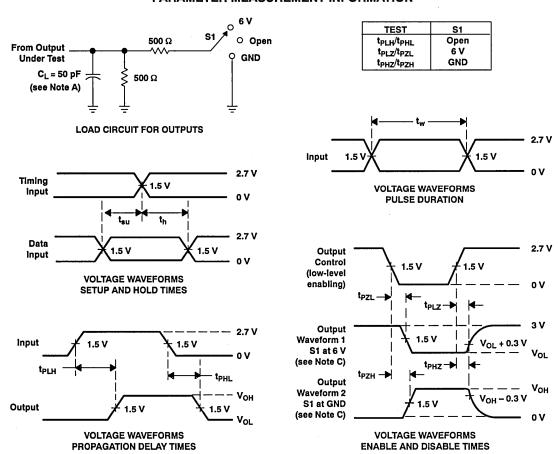

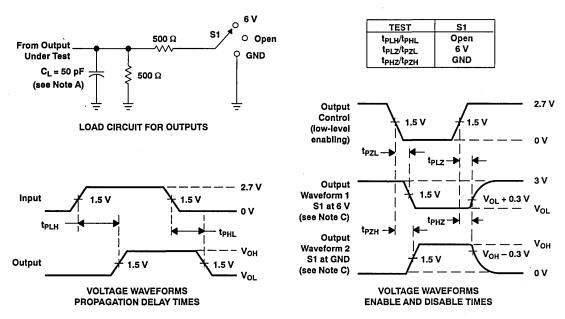

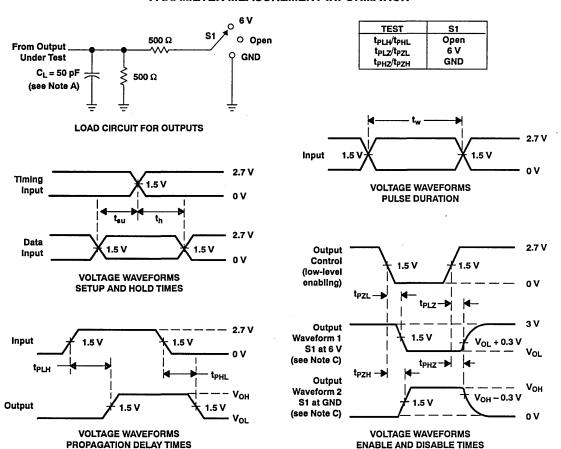

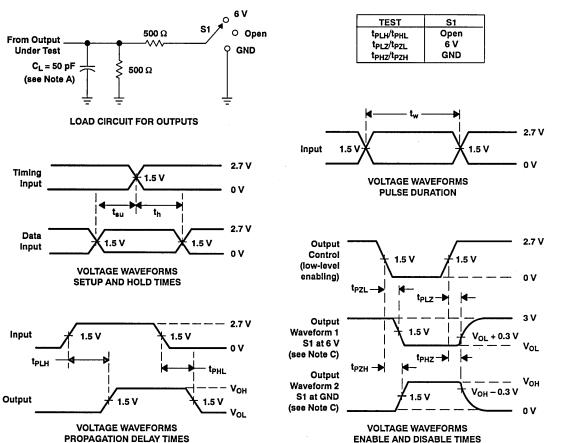

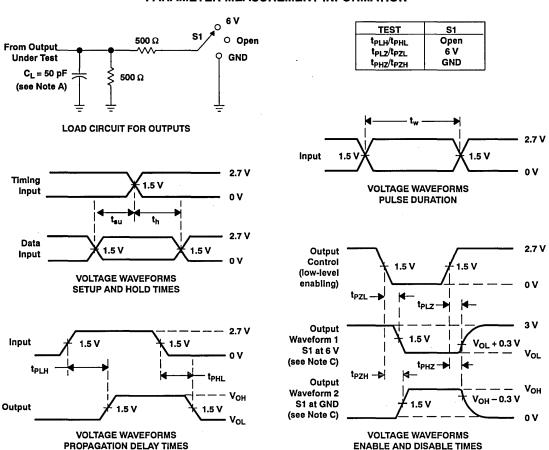

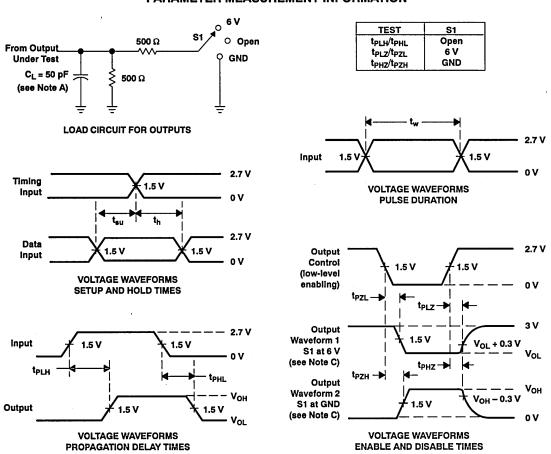

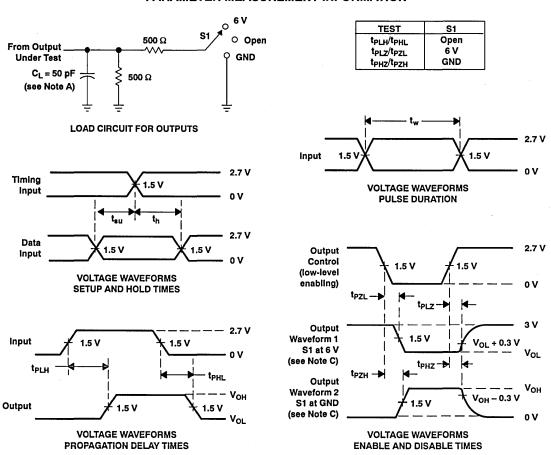

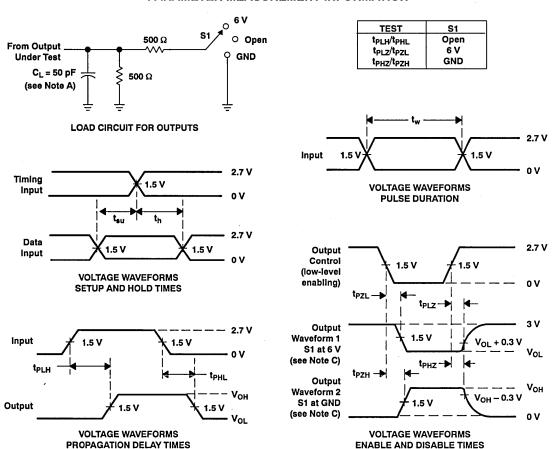

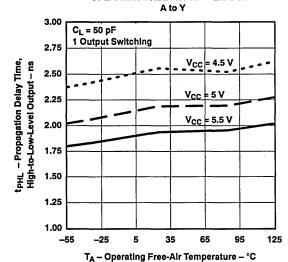

### t<sub>PHL</sub> Propagation delay time, high-to-low level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level.

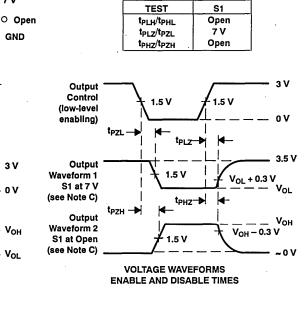

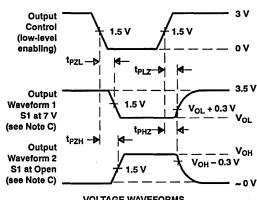

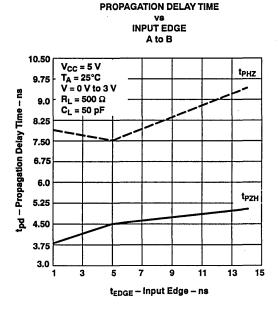

### t<sub>PHZ</sub> Disable time (of a 3-state output) from high level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined high level to a high-impedance (off) state.

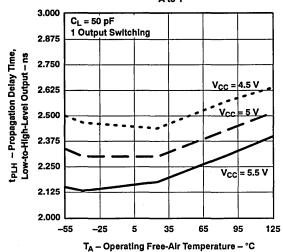

### t<sub>PLH</sub> Propagation delay time, low-to-high level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level.

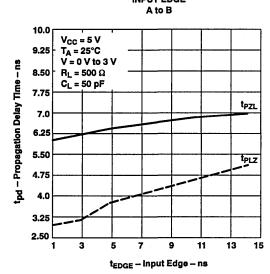

### t<sub>PLZ</sub> Disable time (of a 3-state output) from low level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined low level to a high-impedance (off) state.

### t<sub>PZH</sub> Enable time (of a 3-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to the defined high level.

### t<sub>PZL</sub> Enable time (of a 3-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to the defined low level.

### t<sub>su</sub> Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

- NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- 2. The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

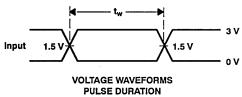

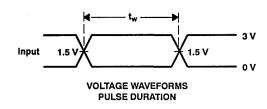

### t<sub>w</sub> Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

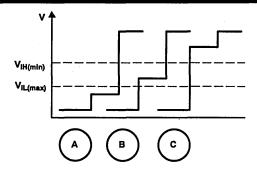

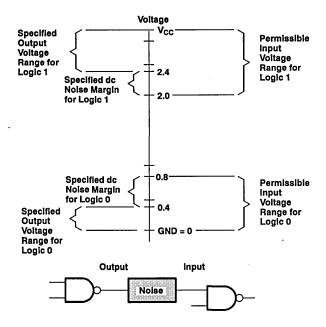

### V<sub>IH</sub> High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is quaranteed.

### V<sub>IL</sub> Low-level input voltage

An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A maximum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is guaranteed.

### V<sub>OH</sub> High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a high level at the output.

### V<sub>OL</sub> Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a low level at the output.

# $V_{T+}$ Positive-going threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage rises from a level below the negative-going threshold voltage,  $V_{T-}$ .

### V<sub>T</sub>... Negative-going threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage falls from a level above the positive-going threshold voltage,  $V_{T+}$ .

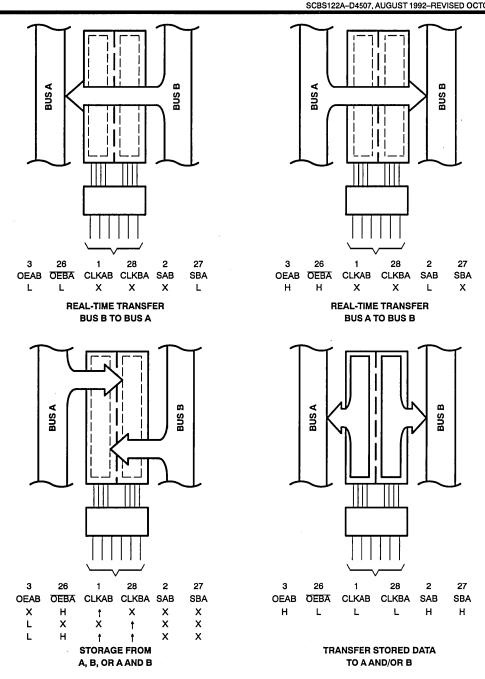

### **EXPLANATION OF FUNCTION TABLES**

The following symbols are used in function tables on TI data sheets:

H = high level (steady state)

L = low level (steady state)

↑ = transition from low to high level ↓ = transition from high to low level

= value/level or resulting value/level is routed to indicated destination

= value/level is re-entered

X = irrelevant (any input, including transitions)

Z = off (high-impedance) state of a 3-state output

a..h = the level of steady-state inputs A through H respectively

Q<sub>0</sub> = level of Q before the indicated steady-state input conditions were established

$\overline{Q}_0$  = complement of  $Q_0$  or level of  $\overline{Q}$  before the indicated steady-state input

conditions were established

$Q_n$  = level of Q before the most recent active transition indicated by  $\downarrow$  or  $\uparrow$

= one high-level pulse

= one low-level pulse

TOGGLE = each output changes to the complement of its previous level on each active

transition indicated by ↓ or ↑

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

If, in the input columns, a row contains H, L, and/or X together with  $\uparrow$  and/or  $\downarrow$ , this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L, Q<sub>0</sub>, or  $\overline{Q}_0$ ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse,  $\neg \neg \neg \neg \neg$ , the pulse follows the indicated input transition and persists for an interval dependent on the circuit.)

Among the most complex function tables are those of the shift registers. These embody most of the symbols used in any of the function tables, plus more. Below is the function table of a 4-bit bidirectional universal shift register, e.g., type SN74194.

**FUNCTION TABLE**

|       |      |    |       | INPUTS |       |   |          |   |   |                 | OUTI              | PUTS              |                |

|-------|------|----|-------|--------|-------|---|----------|---|---|-----------------|-------------------|-------------------|----------------|

| CLEAR | MODE |    | СГОСК | SEI    | RIAL  |   | PARALLEL |   |   |                 |                   |                   | )              |

| CLEAN | S1   | So | CLUCK | LEFT   | RIGHT | Α | В        | С | D | QA              | QB                | QC                | Q <sub>D</sub> |

| L     | X.   | X  | Х     | X      | X     | Х | Х        | Х | Х | L               | L                 | L                 | L              |

| н     | Х    | Х  | L     | x      | Х     | × | Х        | X | Х | Q <sub>AO</sub> | $Q_{B0}$          | $Q_{C0}$          | $Q_{D0}$       |

| H     | Н    | Н  | Ť     | ×      | X     | а | b        | С | d | a               | b                 | С                 | d              |

| н     | L    | Н  | t     | x      | Н     | н | Н        | н | Н | lн              | $\mathbf{Q}_{An}$ | $\mathbf{Q}_{Bn}$ | $Q_{Cn}$       |

| н     | L    | Н  | t     | ×      | L     | L | L        | L | L | l L             | $Q_{An}$          | $Q_{Bn}$          | $Q_{Cn}$       |

| н     | Н    | L  | 1     | н      | X     | x | X        | X | X | Q <sub>Bn</sub> | $Q_{Cn}$          | $Q_{Dn}$          | Н              |

| н     | Н    | L  | t     | L      | X     | x | X        | X | Х | Q <sub>Bn</sub> | $\mathbf{Q}_{Cn}$ | $\mathbf{Q}_{Dn}$ | L              |

| Н     | L    | L  | Х     | Х      | Х     | Х | Х        | Х | Х | Q <sub>A0</sub> | Q <sub>B0</sub>   | $Q_{C0}$          | $Q_{D0}$       |

The first line of the table represents a synchronous clearing of the register and says that if clear is low, all four outputs will be reset low regardless of the other inputs. In the following lines, clear is inactive (high) and so has no effect.

The second line shows that so long as the clock input remains low (while clear is high), no other input has any effect and the outputs maintain the levels they assumed before the steady-state combination of clear high and clock low was established. Since on other lines of the table only the rising transition of the clock is shown to be active, the second line implicitly shows that no further change in the outputs will occur while the clock remains high or on the high-to-low transition of the clock.

The third line of the table represents synchronous parallel loading of the register and says that if S1 and S0 are both high then, without regard to the serial input, the data entered at A will be at output  $Q_A$ , data entered at B will be at  $Q_B$ , and so forth, following a low-to-high clock transition.

The fourth and fifth lines represent the loading of high- and low-level data, respectively, from the shift-right serial input and the shifting of previously entered data one bit; data previously at  $Q_A$  is now at  $Q_B$ , the previous levels of  $Q_B$  and  $Q_C$  are now at  $Q_C$  and  $Q_D$ , respectively, and the data previously at  $Q_D$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is low and S0 is high and the levels at inputs A through D have no effect.

The sixth and seventh lines represent the loading of high- and low-level data, respectively, from the shift-left serial input and the shifting of previously entered data one bit; data previously at  $Q_B$  is not at  $Q_A$ , the previous levels of  $Q_C$  and  $Q_D$  are now at  $Q_B$  and  $Q_C$ , respectively, and the data previously at  $Q_A$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is high and S0 is low and the levels at inputs A through D have no effect.

The last line shows that as long as both inputs are low, no other input has any effect and, as in the second line, the outputs maintain the levels they assumed before the steady-state combination of clear high and both mode inputs low was established.

The function table functional tests do not reflect all possible combinations or sequential modes.

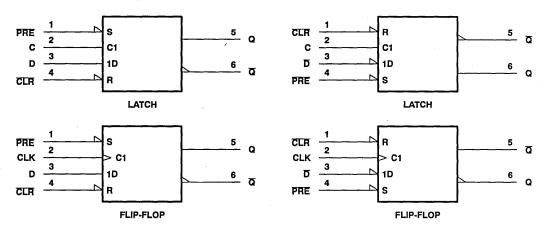

### D FLIP-FLOP AND LATCH SIGNAL CONVENTIONS

It is normal TI practice to name the outputs and other inputs of a D-type flip-flop or latch and to draw its logic symbol based on the assumption of true data (D) inputs. Outputs that produce data in phase with the data inputs are called Q and those producing complementary data are called  $\overline{Q}$ . An input that causes a Q output to go high or a  $\overline{Q}$  output to go low is called preset (PRE). An input that causes a  $\overline{Q}$  output to go high or a Q output to go low is called clear (CLR). Bars are used over these pin names (PRE and CLR) if they are active low.

The devices on several data sheets are second-source designs, and the pin name conventions used by the original manufacturers have been retained. That makes it necessary to designate the inputs and outputs of the inverting circuits  $\overline{D}$  and  $\overline{Q}$ .

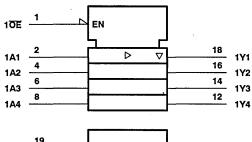

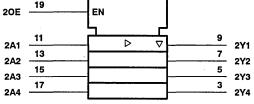

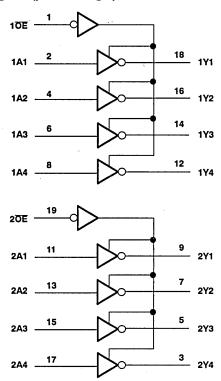

In some applications, it may be advantageous to redesignate the data input from D to D or vice versa. In that case, all the other inputs and outputs should be renamed as shown below. Also shown are corresponding changes in the graphical symbols. Arbitrary pin numbers are shown.

The figures show that when Q and  $\overline{Q}$  exchange names, the preset and clear pins also exchange names. The polarity indicators ( $\triangleright$ ) on PRE and CLR remain, as these inputs are still active-low, but the presence or absence of the polarity indicator changes at D (or  $\overline{D}$ ), Q, and  $\overline{Q}$ . Pin 5 (Q or  $\overline{Q}$ ) is still in phase with the data input (D or  $\overline{D}$ ); their active levels change together.

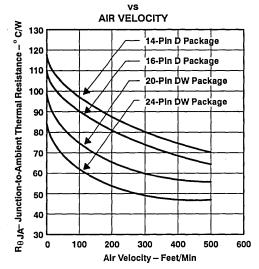

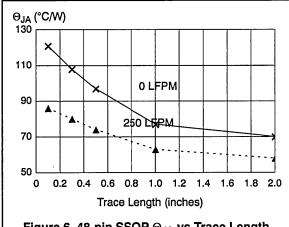

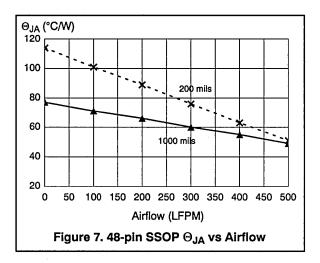

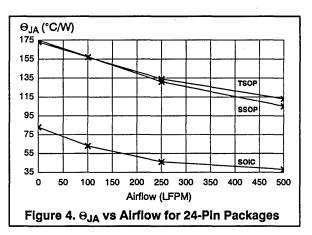

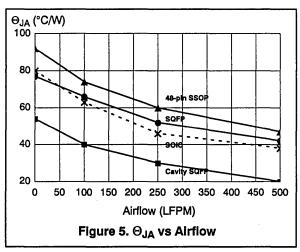

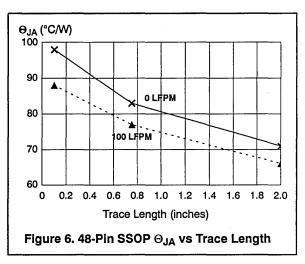

In digital system design, consideration must be given to thermal management of components. The small size of the small-outline package makes this even more critical. Figure 1 shows the thermal resistance of these packages for various rates of air flow.

The thermal resistances in Figure 1 can be used to approximate typical and maximum virtual junction temperatures for the EPIC™ ACL family. In general, the junction temperature for any device can be calculated using Equation 1.

$$T_{.1} = R_{0.1A} \times P_T + T_A \tag{1}$$

where:

virtual junction temperature

thermal resistance, junction to free air total power dissipation of the device

$P_T = V_{CC} \times I_{CC} + (C_{pd} \times V_{CC}^2 \times f_i) + \Sigma(C_i \times V_{CC}^2 \times f_o)$

free-air temperature

The total power consumption can be determined from Equation 2 for an AC device and Equation 3 for an ACT device.

Figure 1

(2)

(3)

$$P_T = V_{CC} \times [I_{CC} + (N \times \Delta I_{CC} \times dc)] + (C_{pd} \times V_{CC}^2 \times f_i) + \Sigma(C_L \times V_{CC}^2 \times f_o)$$

where:

$V_{CC}$ supply voltage (5 V for typical, 5.5 V for maximum) (see Note 1)

quiescent supply current (specified on device data sheet) lcc power dissipation capacitance (from the device data sheet) =

input frequency

output load capacitance

output frequency

fo N number of inputs driven by a TTL device

dc duty cycle

increase in supply current (specified on device data sheet) Δlcc

NOTE 1: In system applications, I<sub>CC</sub> can be minimized by keeping input voltage levels less than 1 V for V<sub>IL</sub> and greater than V<sub>CC</sub>-1 V for V<sub>IH</sub> and input rise and fall times less than 15 ns.

The following tables outline the logic functions Texas Instruments offers in a variety of technologies. The tables are organized by function type and list all available or planned options of that function. The technology columns identify the appropriate family and a particular data book where more information can be found. The applicable literature number, composed of either seven or eight alphanumeric characters, can be found at the lower right-hand corner on the back cover of each publication.

List of additional General Purpose Logic data books:

| AC and ACT Devices         | Advanced CMOS Logic Data Book                    | SCAD001C |

|----------------------------|--------------------------------------------------|----------|

| Advanced Logic Devices     | Advanced Logic and Bus Interface Logic Data Book | SCYD001  |

| ALS and AS Devices         | ALS/AS Logic Data Book                           | SDAD001B |

| BCT Devices                | BiCMOS Bus Interface Logic Data Book             | SCBD001A |

| F Devices                  | F Logic (54/74F) Data Book                       | SDFD001B |

| FIFO Devices               | High-Performance FIFO Memories Data Book         | SCAD003  |

| HC and HCT Devices         | High-Speed CMOS Logic Data Book                  | SCLD001C |

| SCOPE™ Devices             | SCOPE™ Product Information                       | SSYV001  |

| Std TTL, LS, and S Devices | TTL Logic Data Book                              | SDLD001A |

### Contents

| Page                                                                   | , |

|------------------------------------------------------------------------|---|

| GATES 1–14                                                             |   |

| Positive-NAND Gates1–14                                                |   |

| Positive-AND Gates1–14                                                 |   |

| Positive-OR/NOR Gates115                                               |   |

| OR/NOR Gates 1–15                                                      |   |

| AND-OR Gates 1–15                                                      |   |

| INVERTING/NONINVERTING BUFFERS 1–16                                    |   |

| Hex Inverters/Noninverters1–16                                         |   |

| BUFFERS/DRIVERS AND BUS TRANSCEIVERS                                   |   |

| Buffers/Drivers                                                        |   |

| Universal Bus Transceivers (UBT™)/Universal Bus Exchangers (UBE™) 1–18 |   |

| Bus Transceivers 1–19                                                  |   |

| MOS Memory Drivers/Transceivers                                        |   |

| TESTABILITY BUS-INTERFACE CIRCUITS                                     |   |

| SCOPE™ Testability Circuits                                            | , |

| FLIP-FLOPS AND LATCHES1–24                                             |   |

| Flip-Flops 1–24                                                        |   |

| Latches 1–26                                                           |   |

| Contents (continued)                                              | _             |

|-------------------------------------------------------------------|---------------|

|                                                                   | Page          |

| REGISTERS                                                         |               |

| Shift Registers                                                   |               |

| Register Files                                                    | 1–27          |

| COUNTERS                                                          | 1–28          |

| Synchronous Counters – Positive-Edge-Triggered                    | 1–28          |

| Asynchronous Counters (Ripple Clock) - Negative-Edge-Triggered    | 1–28          |

| 8-Bit Binary Counters With Registers                              | 1–28          |

| DECODERS, ENCODERS, DATA SELECTORS/MULTIPLEXERS                   | I <b>–</b> 29 |

| Encoders/Data Selectors/Multiplexers                              | 1–29          |

| Decoders/Demultiplexers                                           | 1–30          |

| Shifters 1                                                        | 1–30          |

| COMPARATORS AND PARITY GENERATORS/CHECKERS                        | 1–31          |

| Comparators                                                       | 1–31          |

| Address Comparators                                               | 1–31          |

| Parity Generators/Checkers                                        | 1–31          |

| ARITHMETIC CIRCUITS AND FIFO MEMORIES                             | 1–32          |

| Parallel Binary Adders 1                                          | 1–32          |

| Accumulators, Arithmetic Logic Units, Look-Ahead Carry Generators | 1–32          |

| First-In, First-Out Memories (FIFOs)                              | 1–32          |

| CLOCK DRIVER CIRCUITS                                             | 1–33          |

| Clock Drivers                                                     | 1–33          |

| ECL TRANSLATORS                                                   |               |

| ECL to TTL or TTL to ECL Translators                              |               |

### **GATES**

### **Positive-NAND Gates**

| DESCRIPTION      | OUTPUT | TYPE   | TECHNOLOGY |    |   |    |     |    |     |     |     |

|------------------|--------|--------|------------|----|---|----|-----|----|-----|-----|-----|

| DESCRIPTION      | OUIPUI |        | ALS        | AS | F | НС | нст | AC | ACT | вст | ABT |

| 8-Input          |        | '30    | ~          | ~  | ~ | ~  | 1   |    |     |     |     |

| 8-input          |        | '11030 |            |    | , |    | 1   | ~  | ~   | ļ — |     |

| 13-input         | L      | '133   | ~          |    |   | V  |     |    |     |     |     |

| Dual 2-Input     |        | '8003  | V          |    |   |    | 1   |    | Ţ   | 1   | 1   |

| Dual 4-Input     |        | '11013 |            |    |   |    |     | V  | Ţ   |     |     |

|                  |        | '20    | V          | ~  | V | ~  |     |    |     |     |     |

|                  |        | '40    | V          |    | ~ |    |     |    |     |     |     |

|                  |        | '11020 |            |    |   |    |     | ~  | ~   |     |     |

| Triple 3-Input   |        | '10    | ~          | V  | ~ | ~  |     |    |     |     |     |

|                  |        | '1010  | ~          |    |   |    |     |    |     |     |     |

|                  |        | '11010 |            |    |   |    |     | V  | ~   |     |     |

|                  |        | '00    | ~          | ~  | V | V  | ~   |    |     |     |     |

|                  |        | '11000 |            |    |   |    |     | ~  | ~   |     |     |

|                  |        | '37    | ~          |    |   |    |     |    |     |     |     |

| Quad 2-Input     | ос     | '38    | ~          |    | V |    |     |    |     |     |     |

|                  |        | '132   |            |    |   | V  |     |    |     |     |     |

|                  |        | '11132 |            |    |   |    |     | ~  | V   |     |     |

| •                |        | '1000  |            | ~  |   |    |     |    |     |     |     |

| Llau O launt     |        | '804   | ~          | ~  |   |    |     |    |     |     |     |

| Hex 2-Input      |        | '1804  |            | ~  |   |    |     |    | 1   |     |     |

| Over d.O. leaved | 00     | '01    | ~          |    |   | ~  |     |    |     |     |     |

| Quad 2-Input     | ос     | '03    | V          |    |   | V  |     | }  |     |     |     |

### **Positive-AND Gates**

| DESCRIPTION    | ОИТРИТ | 7/05   | TECHNOLOGY |    |          |    |     |    |     |     |     |

|----------------|--------|--------|------------|----|----------|----|-----|----|-----|-----|-----|

|                |        | TYPE   | ALS        | AS | F        | НС | нст | AC | ACT | BCT | ABT |

| Triple 3-Input | ос     | '15    | ~          |    |          |    |     |    |     |     |     |

| 0              | ос     | '09    | ~          |    |          | ~  |     |    |     |     |     |

| Quad 2-input   |        | '7001  |            |    |          | ~  |     |    |     |     |     |

| Dual 4-Input   |        | '21    | ~          | ~  | V        | ~  |     |    |     |     |     |

|                |        | '11021 |            |    |          |    |     | ~  | ~   |     |     |

| Talala O lanas |        | '11    | ~          | V  | V        | V  |     |    |     |     |     |

| Triple 3-Input |        | '11011 |            |    |          |    | 1   | V  | V   |     |     |

|                |        | '08    | ~          | ~  | ~        | ~  | V   |    |     |     |     |

| Quad 2-Input   |        | '1008  |            | ~  |          |    |     |    |     |     |     |

| •              |        | '11008 |            |    |          |    |     | ~  | 1   |     |     |

|                |        | '808   |            | V  |          | V  |     |    |     |     |     |

| Hex 2-Input    |        | '1808  |            | V  | <u> </u> |    |     |    |     |     |     |

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

# **GATES** (continued)

### Positive-OR/NOR Gates

| DECODINE       | CUITDUIT | 700    |     |    |   | Т  | ECHNOLO | ΒY |     |     |     |

|----------------|----------|--------|-----|----|---|----|---------|----|-----|-----|-----|

| DESCRIPTION    | OUTPUT   | TYPE   | ALS | AS | F | нс | нст     | AC | ACT | ВСТ | ABT |

| Triple 3-Input |          | '4075  |     |    |   | V  |         |    |     |     |     |

|                |          | '32    | ~   | ~  | V | V  | V       |    |     |     | ]   |

| Ound Olemen    |          | '1032  |     | ~  |   |    |         |    |     |     |     |

| Quad 2-Input   |          | '11032 |     | -  |   |    |         | V  | V : |     |     |

|                |          | '7032  |     |    |   | V  |         |    |     |     |     |

| Llau O la aut  |          | '832   | ~   | ~  |   | V  |         |    |     |     |     |

| Hex 2-Input    |          | '1832  |     | ~  |   |    |         |    |     |     |     |

| Dual 5-Input   |          | '260   |     |    | V |    |         |    |     |     |     |

|                |          | '27    | ~   |    | V | V  |         |    |     |     |     |

| Triple 3-Input |          | '11027 |     |    |   |    |         | V  | V   |     |     |

|                |          | '02    | ~   | ~  | V | V  | ~       |    |     |     |     |

|                | ос       | '33    | ~   |    |   |    |         |    |     |     |     |

| Quad 2-Input   |          | '36    |     |    | ~ | ~  |         |    |     |     |     |

|                |          | 7002   |     |    |   | ~  |         |    |     |     |     |

|                |          | '11002 |     |    |   |    |         | V  | V   |     |     |

| Nov. O. Immust |          | '805   | ~   | ~  |   |    |         |    |     |     |     |

| ex 2-Input     |          | '1805  |     | V  |   |    |         | l  |     |     |     |

### **OR/NOR Gates**

| DESCRIPTION                         | OUTPUT | TYPE   |     |    |   | TE | CHNOLO | GY |     |     | -   |

|-------------------------------------|--------|--------|-----|----|---|----|--------|----|-----|-----|-----|

| DESCRIPTION                         | OUIPUI | ITPE   | ALS | AS | F | нс | нст    | AC | ACT | вст | ABT |

| 8-Input                             |        | '4078  |     |    |   | ~  |        |    | Ţ   |     |     |

| Quad 2-Input                        |        | '86    | ~   | ~  | ~ | ~  |        |    |     |     |     |

| Exclusive-OR Gates                  |        | '11086 |     |    |   |    |        | 1  | ~   |     |     |

| With Totem-Pole Outputs             |        | '386   |     |    |   | ~  |        |    |     |     |     |

| Quad 2-Input<br>Exclusive-OR Gates  | ос     | '136   | ~   |    |   |    |        |    |     |     |     |

|                                     | OD     | '266   |     |    |   | V  |        |    | 1   |     |     |

|                                     |        | '810   | V   |    |   | T  | T      |    |     |     |     |

| Quad 2-Input<br>Exclusive-NOR Gates |        | '11810 |     |    |   |    |        | ~  | V   |     |     |

| LXCIUSIVO-INOTI GALOS               |        | '7266  |     |    |   | V  |        |    | 1   |     |     |

|                                     | ОС     | '811   | V   |    |   |    |        |    |     |     |     |

### **AND-OR Gates**

| DESCRIPTION                  | OUTPUT | TYPE |     |    |   | TE | CHNOLO | GY |     |     |     |

|------------------------------|--------|------|-----|----|---|----|--------|----|-----|-----|-----|

| DESCRIPTION                  | COIPOI | ITPE | ALS | AS | F | HC | HCT    | AC | ACT | вст | ABT |

| Quad 4-2-3-2-Wide Input      |        | '64  |     |    | ~ |    |        |    |     |     |     |

| Dual 2-Wide 2-Input, 3-Input |        | '51  |     |    | ~ | V  |        |    |     |     |     |

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

### **INVERTING/NONINVERTING BUFFERS**

### Hex Inverters/Noninverters

| DECORPORION         | OUTDUT | 700    |     |    |   |    | TECHN | OLOGY |    |     |     |     |

|---------------------|--------|--------|-----|----|---|----|-------|-------|----|-----|-----|-----|

| DESCRIPTION         | OUTPUT | TYPE   | ALS | AS | F | HC | НСТ   | HCU   | AC | ACT | вст | ABT |

|                     |        | '04    | ~   | ~  | V | V  | V     | V     |    | T   |     |     |

|                     |        | '11004 |     |    |   |    |       |       | V  | V   |     |     |

|                     | ос     | '05    | ~   |    |   | V  |       |       |    |     |     |     |

| Hex Inverters       |        | '14    |     |    |   | V  |       |       |    |     |     |     |

|                     |        | '11014 |     |    |   |    |       |       | ~  | V   |     |     |

|                     |        | '1004  | ~   | ~  |   |    |       |       |    |     |     |     |

|                     |        | '1005  | ~   |    |   |    |       |       |    |     |     |     |

|                     |        | '34    | ~   |    |   |    |       |       |    |     |     |     |

|                     |        | '11034 |     |    |   |    |       |       | ~  | ~   |     |     |

| dex<br>Noninverters | ос     | '35    | ~   |    |   |    |       |       |    |     |     |     |

|                     |        | '1034  | ~   | ~  |   |    |       |       |    |     |     |     |

|                     | ОС     | 1035   | V   |    |   | 1  | 1     |       |    | 1   |     |     |

### NOTES:

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

### **BUFFERS/DRIVERS AND BUS TRANSCEIVERS**

## **Buffers/Drivers**

| DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ОИТРИТ       | TYPE   |                                                  |    |          |                                                  | TECHN                                            | OLOGY                                   |          |                                                  |     |                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|--------------------------------------------------|----|----------|--------------------------------------------------|--------------------------------------------------|-----------------------------------------|----------|--------------------------------------------------|-----|--------------------------------------------------|

| DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | OUIPUI       | ITPE   | ALS                                              | AS | F        | HC                                               | нст                                              | AC                                      | ACT      | вст                                              | ABT | LVT                                              |

| Quad Buffers/Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38           | '125   |                                                  |    | V        | ~                                                | 1                                                |                                         |          | V                                                | +   | ~                                                |

| Quad Bullers/Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35           | '126   |                                                  |    | ~        | V                                                | ~                                                |                                         |          | V                                                | +   |                                                  |

| Naminusting How Buffers / Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38           | '365   |                                                  |    |          | ~                                                |                                                  |                                         |          |                                                  |     |                                                  |

| Noninverting Hex Buffers/Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35           | '367   |                                                  |    |          | V                                                |                                                  |                                         |          |                                                  |     |                                                  |